Tool/software:

Dear forum users,

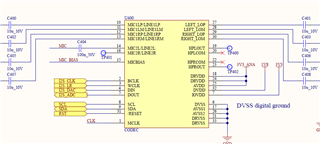

I would like to use TLV320AIC3104 IC for music playing and voice recording.

I connect a Feasycom bluetooth module to the codec via I2S. The clock source for the codec is the BCLK from the bluetooth module. I use Internal PLL to get the correct clock for ADC and DAC.

Audio data is configured for 48khz, 32 bit, stereo.

Playing seems to be working fine, playing a sine wave works.

I connected sine wave (line level output of celllphone) to the MIC2L/LINE2L input.

Issue1: Bluetooth module only generates clock if there is a recording or playing. It seems that configuring PGA requires clock. I can configure DAC, output drivers, I2S parameters without clock, but PGAs gain doesn't change if there is no clock. I would like to make configuration after booting my device, before any bluetooth connection. Am I doing something wrong, or this is normal behaviour? I can't find this information in the datasheet.(I checked PGA operation with routing PGA output to lineout)

Issue2: while recording, I hear creaking and chunky sound instead of clear sine wave. I configure registers during active Bluetooth connection to make sure that TLV320 has clock. I tried to route same signal to left and right ADC too, but did not helped.

Here is my configuration for checking PGA:

0: 0

2: 0

3: 0b10000001

4: 32 << 2

7: 0b00001010

9: 0b00110000

10: 1

11: 1

86: 0b00001001

93: 0b10011001

101: 0

102: 0b10100010

81: 0b10000000

17: 0b00001111

15: 0b01000001

Here is my configuration for checking recording:

0: 0

2: 0

3: 0b10000001

4: 32 << 2

7: 0b00001010

9: 0b00110000

10: 1

11: 1

101: 0

102: 0b10100010

17: 0b00001111

19: 0b11111111

15: 0b01000001

Sine wave is connected to "MIC" label now for testing.