Tool/software:

Hello team,

could you help check below two question:

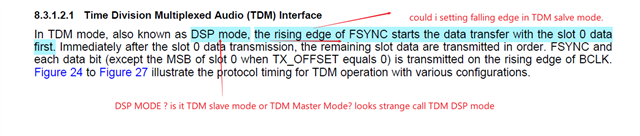

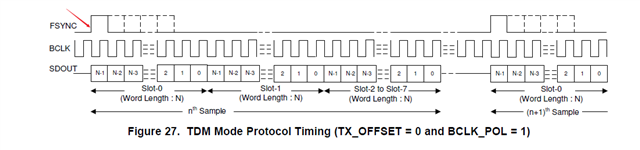

1、In PCM6240 datasheet , TDM as DSP mode, how to understand DSP mode? Is it TDM slave or TDM master? Not clearly description in datasheet.

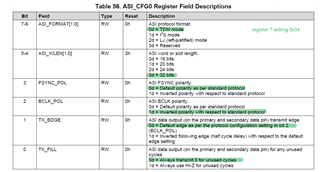

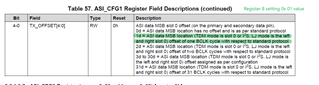

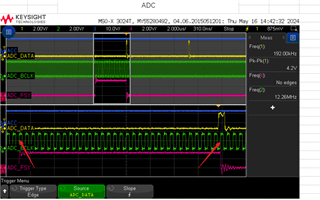

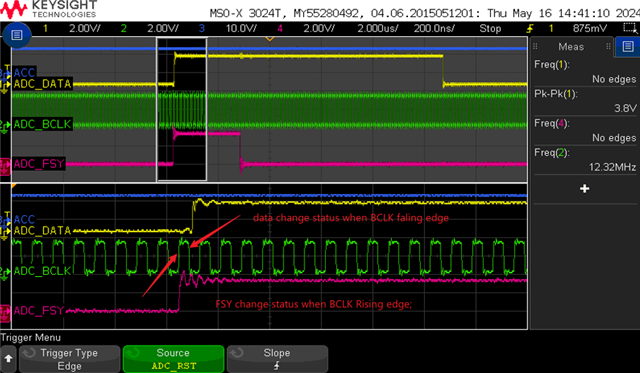

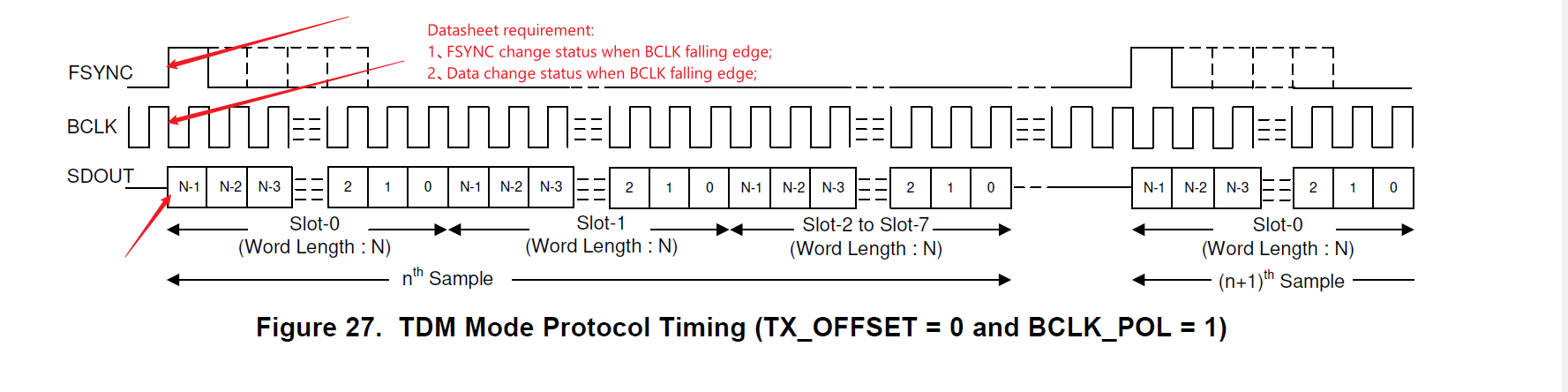

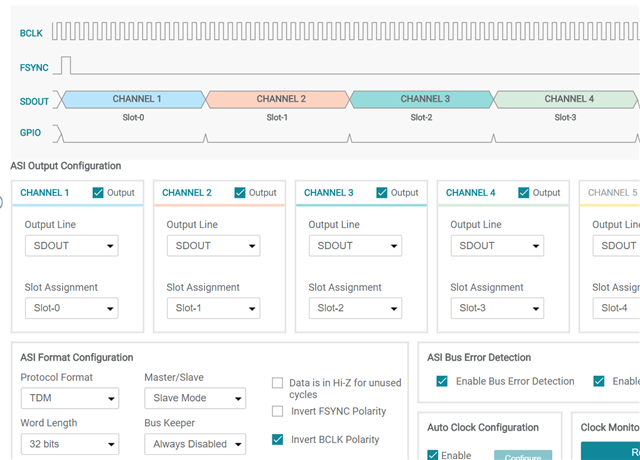

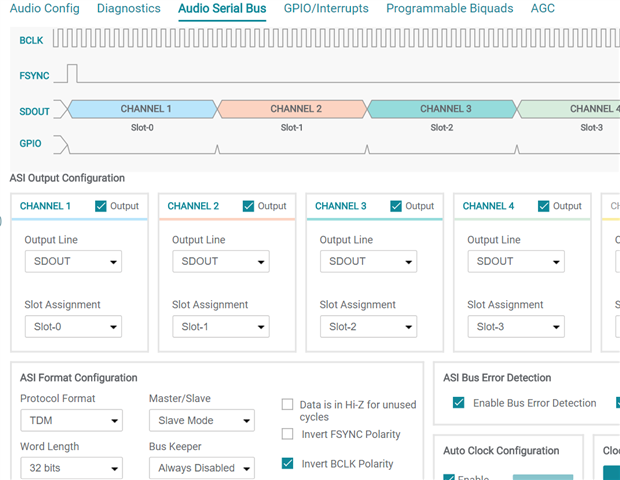

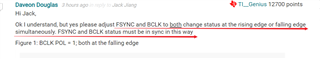

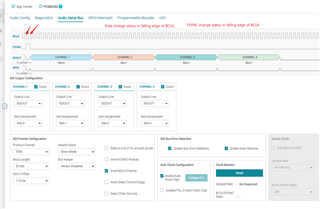

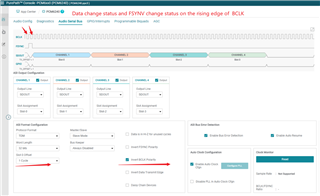

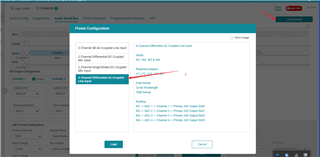

2、coud i setting falling edge of FSYNC starts the data transfer? Our application is ADC as slave , SOC as TDM Master. ADC register 0X07 address setting to 0x34 value;

in datasheet , i think it is just example below, actually , it can be flexible setting by SOC . My understaning is correct?

Thanks