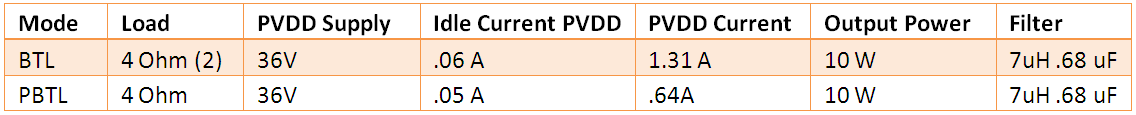

I have an application which is current consumption critical; I am looking at using the TAS5613- for a larger amplifier i want both halves of device, but I want a common part in a lower power application so I only have 1 pcba

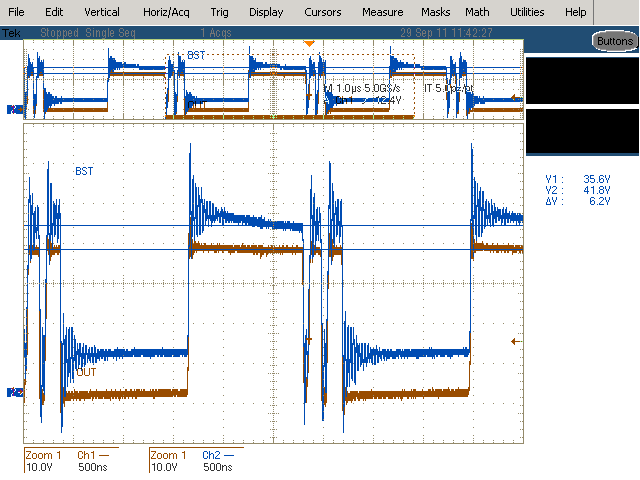

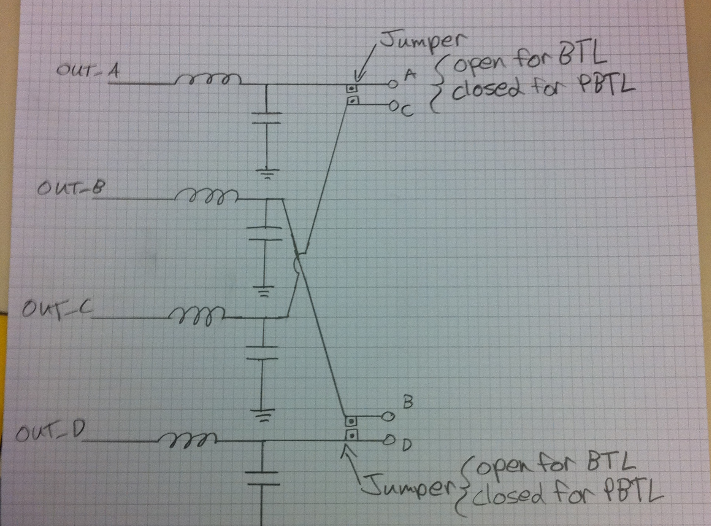

The data sheet states that the UVLO for the bootstrap supply shuts down the half bridge affected, and does not assert the ^SD pin- this is ideal for shutting down C+D half bridges- what is a simple safe way of doing this?

I thought of leaving off Cboot for each half bridge? Or tying boot pin to output with resistor so it is never higher than Vout?

Any help appreciated, I want to commit to pcb soon to try above, better if someone knows though!

regards