Tool/software:

Dears,

Customer have an question about BCK frequency

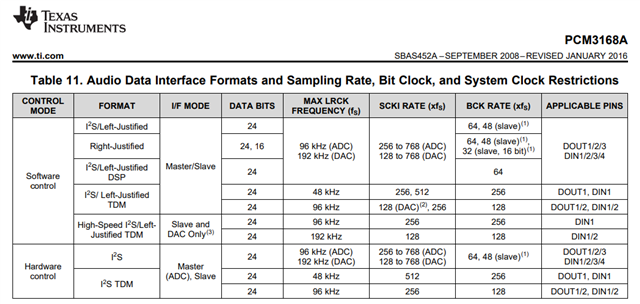

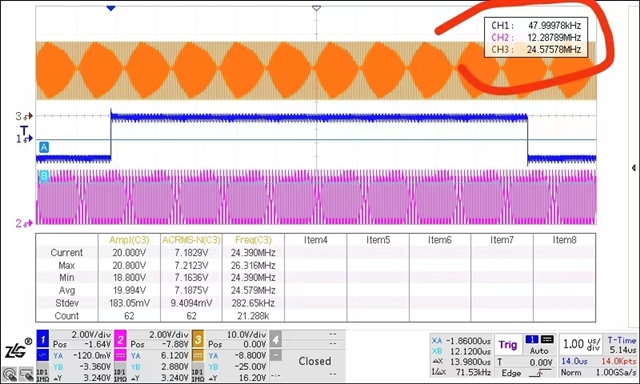

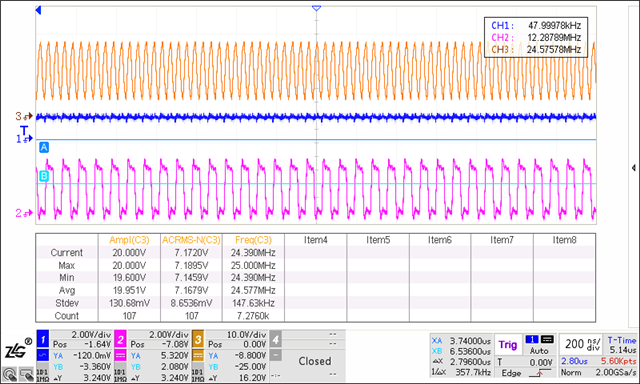

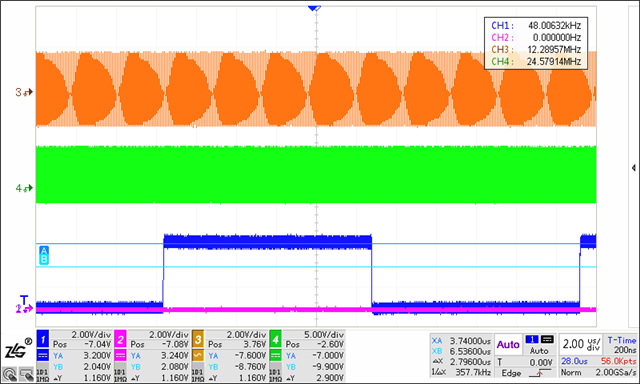

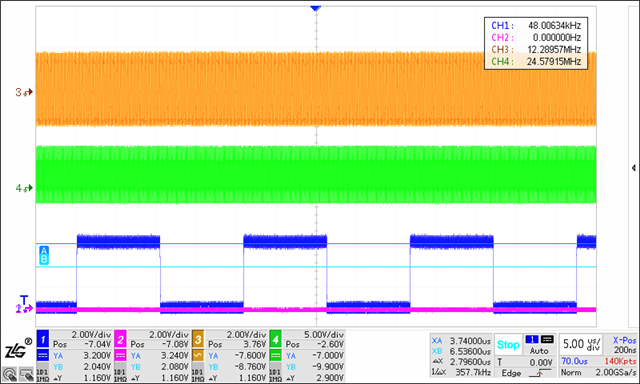

they choose external=24.576MHZ data=32bit 8ch, ADC master, DAC slave, ADC single rate, DAC sample mode Auto, I2C control, normal I2S format no TDM; The output of BCK is 3.072MHZ=64fs;

customer want to BCK 12.288MHZ=256fs;

In I2C control, need fs=192KHZ;

But in hardware control can generate BCK 12.288MHZ when fs=48KHZ;

How to generate BCK=12.288MHZ in normal I2S format no TDM and I2C control mode?

Why the hardware control can generate on these mode?