Tool/software:

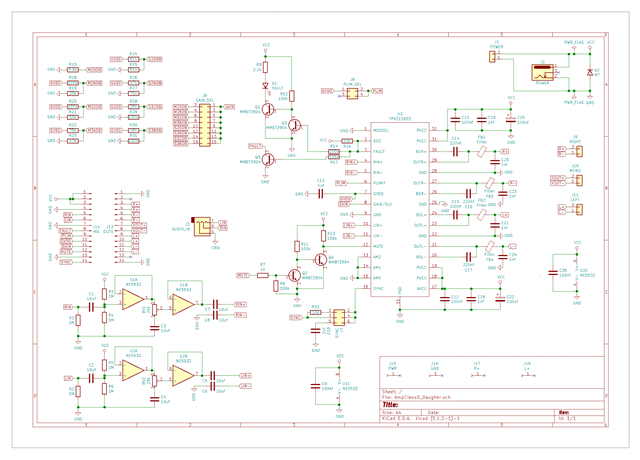

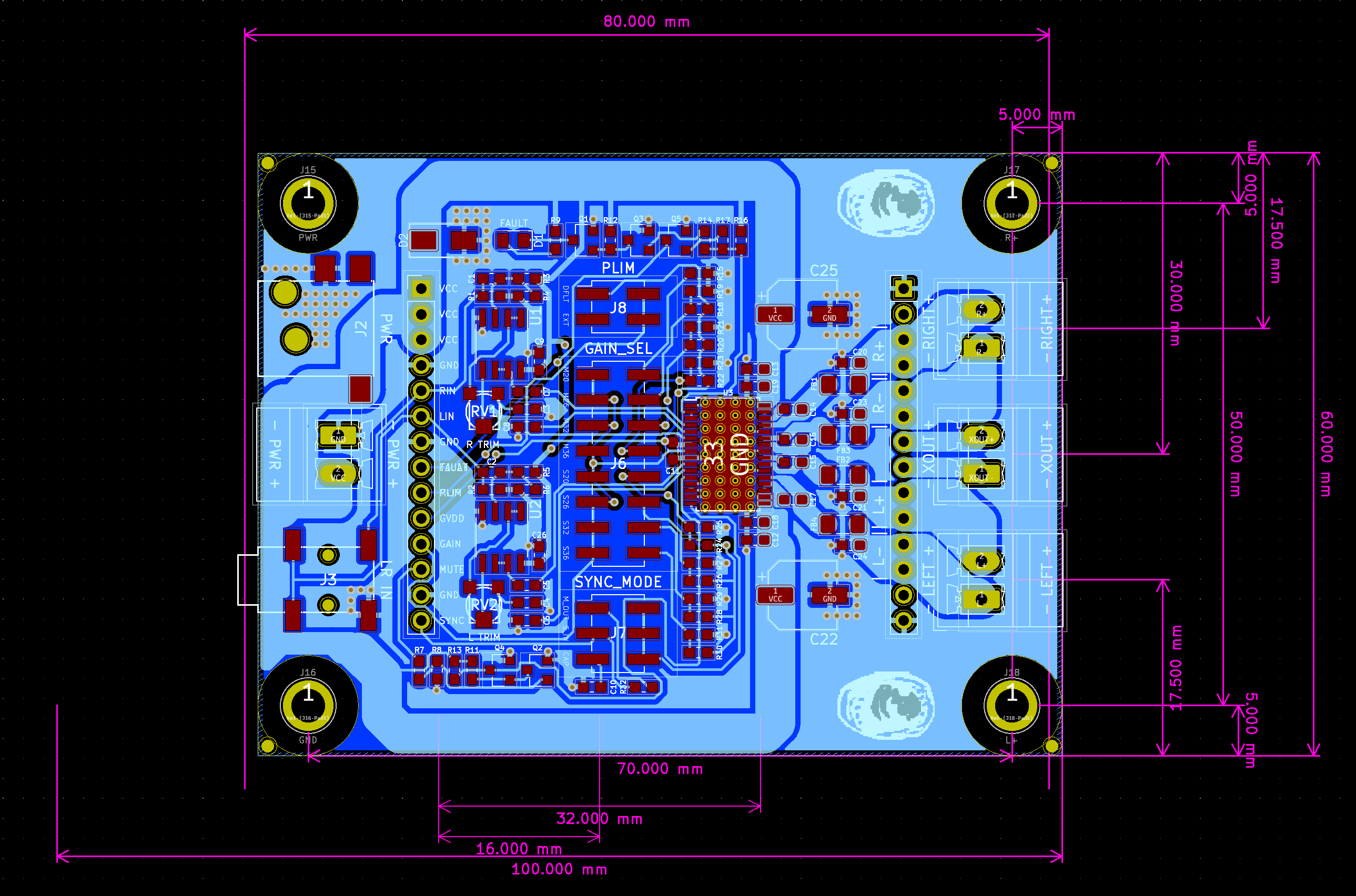

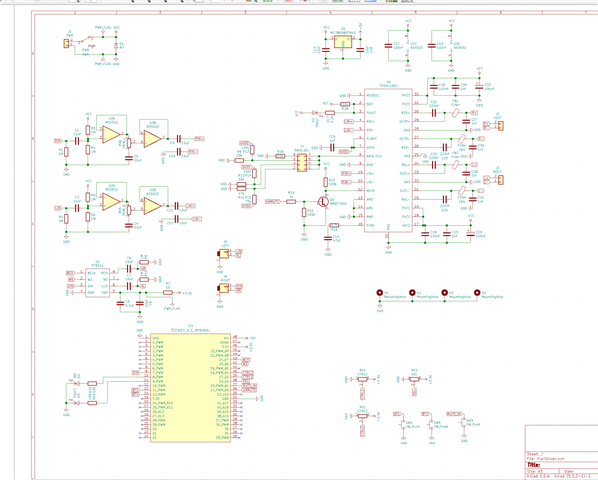

Hi, I have a design using the TPA3118D2 class D amplifier chip. The design is configured with mulitple chips as daughter cards, and a motherboard where they can be connected with one design as the master timing source and 3 other devices as the slaves for sync mode.

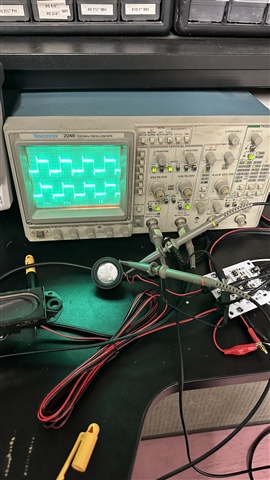

I notice that the master devices gets very hot, whether or not a speaker is plugged in, whereas the slave devices stay cool, regardless of whether a speaker is plugged in. This also occurs when I am using a single chip by itself, as this is used in timing master configuration. The master devices still work and the audio sounds fine, but I would like to eliminate this excessive heat from my design if possible.

Is there some sort of layout or schematic issue that might be causing this?

Please find my design schematic and layout attached. You can also view the complete KiCad project for my design here: github.com/.../V2.0