Tool/software:

Hello, I currently have two TAS2505 which I am planning to use for stereo sound playback. I was studying the I2C example configurations (TAS2505 Application Reference Guide Section 5.1 Example Register Setup to Play Digital Data Through DAC and Headphone/Speaker Outputs) and have some questions:

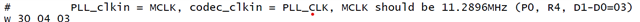

1. I noticed it was said that clock source needs to be 11.2896MHz. The maximum clock frequencies our master chip can support is 4MHz, and I was wondering if it is still able to drive the TAS2505. If so, how should I configure the registers to change up the clock frequency?

2. Preferably, we would like to use other clocks (e.g. SCLK) as the codec's clock source. I was wondering how I should configure the registers to achieve that. Also, if we can use other clock sources, it would provide even slower frequency. I was wondering what the minimum frequency required to drive TAS2505.

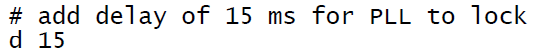

3. There's one line that says a delay of 15 ms is needed. This is way too much for our application which requires the sound to be generated within less than 4ms. Are there any workarounds?

4. For the two of the TAS2505 IC's that we have, we would like to set up one of the them to play I2S data on the left sound channel and the other to be for the right sound channel. The closest thing I could find from the reference guide to achieve this is to set register 63 bits D5-D4 on page 0. I wanted to confirm if this is correct.

Thank you,

--Jiahe Liu