Tool/software:

Hi,

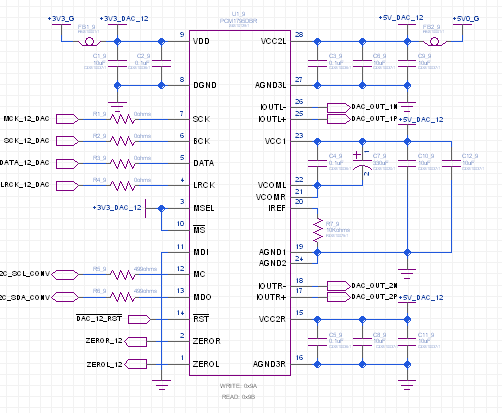

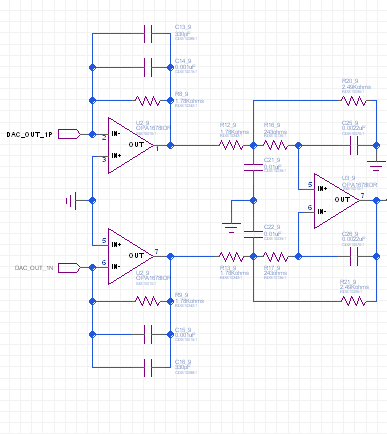

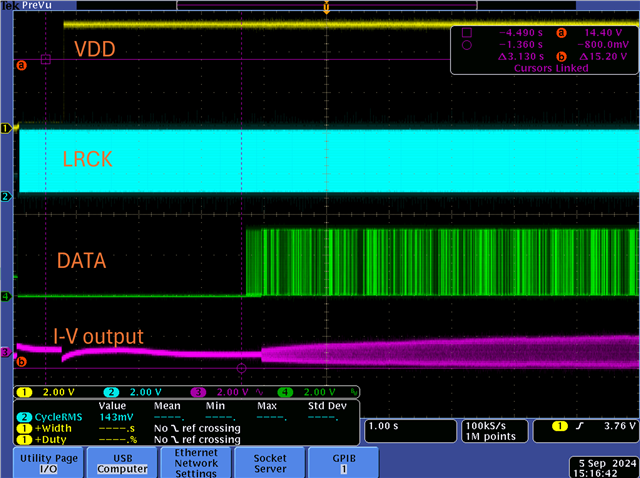

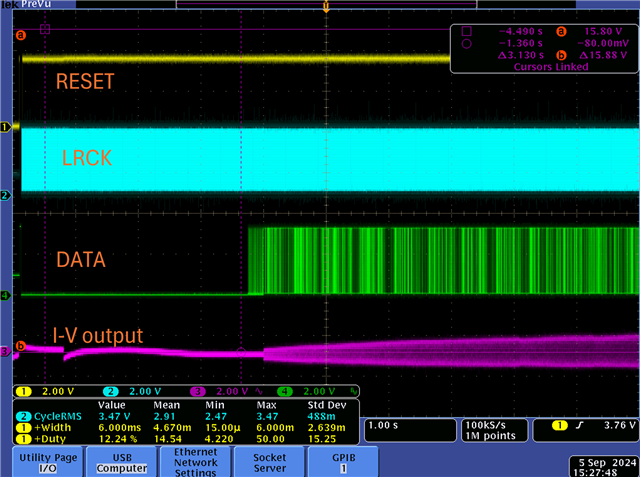

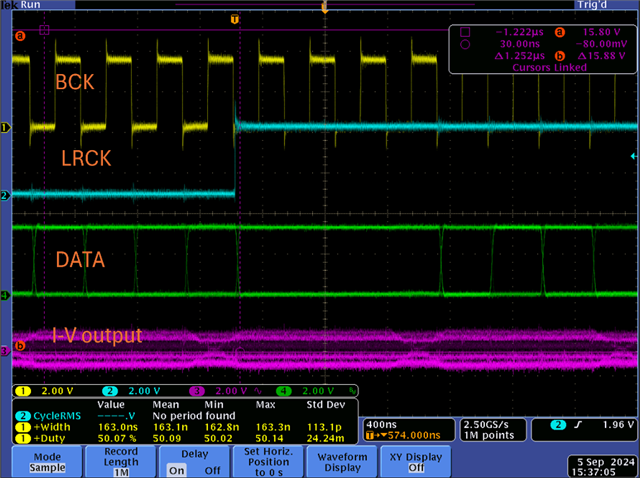

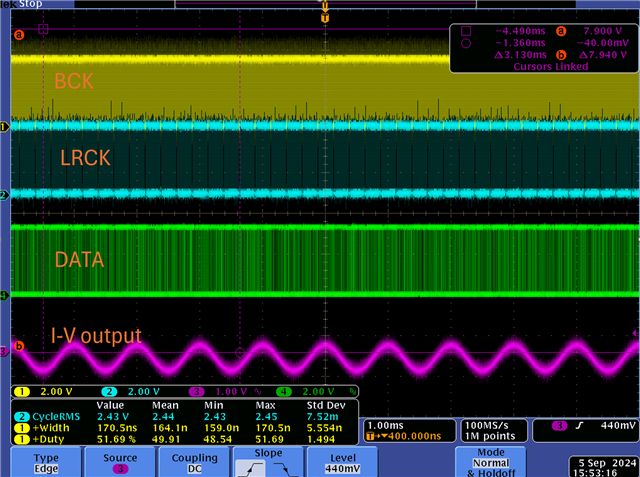

I have a customer who is using this device in a new project and is seeing a long ramp up from zero to full output (3 seconds or more).

There doesn't appear to be an explanation in the datasheet, would you be able to help us understand what is causing this?