Hi,

Could you please describe the recommended power on/off sequence and procedure of the register access for TAS5538?

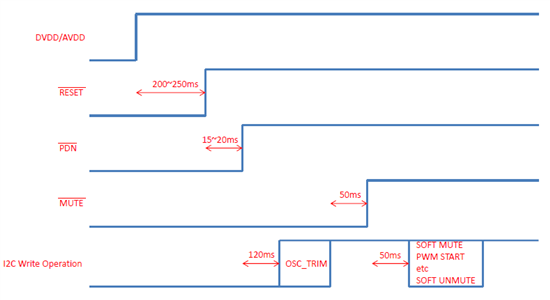

I would like to obtain the information like the timing chart that is described on page 30 to 31 of TAS5731 data sheet.

In addition, could please add the behaviors of RESET, PDN and MUTE pins and the procedure of the register access to the timing chart(soft mute, pwm start, soft unmute, etc.)?

Best Regards,

Kato