Other Parts Discussed in Thread: TLV320AIC3204,

Hi,

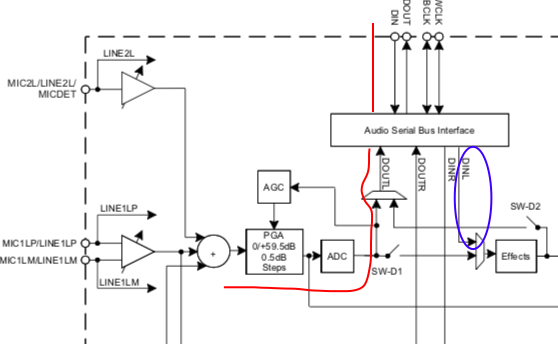

I have some doubts about the functionality of the AGC. We have a device which measures noise and use this codec to measure it. The way of measurement noise is reading the value of the AGC according to the quantity of noise read by the microphone, that is connected to a channel of the codec.

The register of the preamp (R19) is set to 0, the AGC is enabled and its target level is set to -24db. At first sight, every registers ared defined to obtain the maximum gain. The problem we have is that this codec is also used in other device with the same configuration of the registers, but in this case the microphone has a membrane that slightly attenuates the noise, so I would like to calibrate this measure.

The datasheet talks about the algorithm of the AGC. I guess that this algorithm fix the relation between input of the AGC ante output. Is there any way to access to this algorithm?