Other Parts Discussed in Thread: TAS5414

I began a TAS5414/5424 design a while back with the support of the esteemed TI engineer Greg Scott. Excellent TI tech support! Greg was on his game.

Client's upper management tabled this project but recently put it back on my agenda with great urgency.

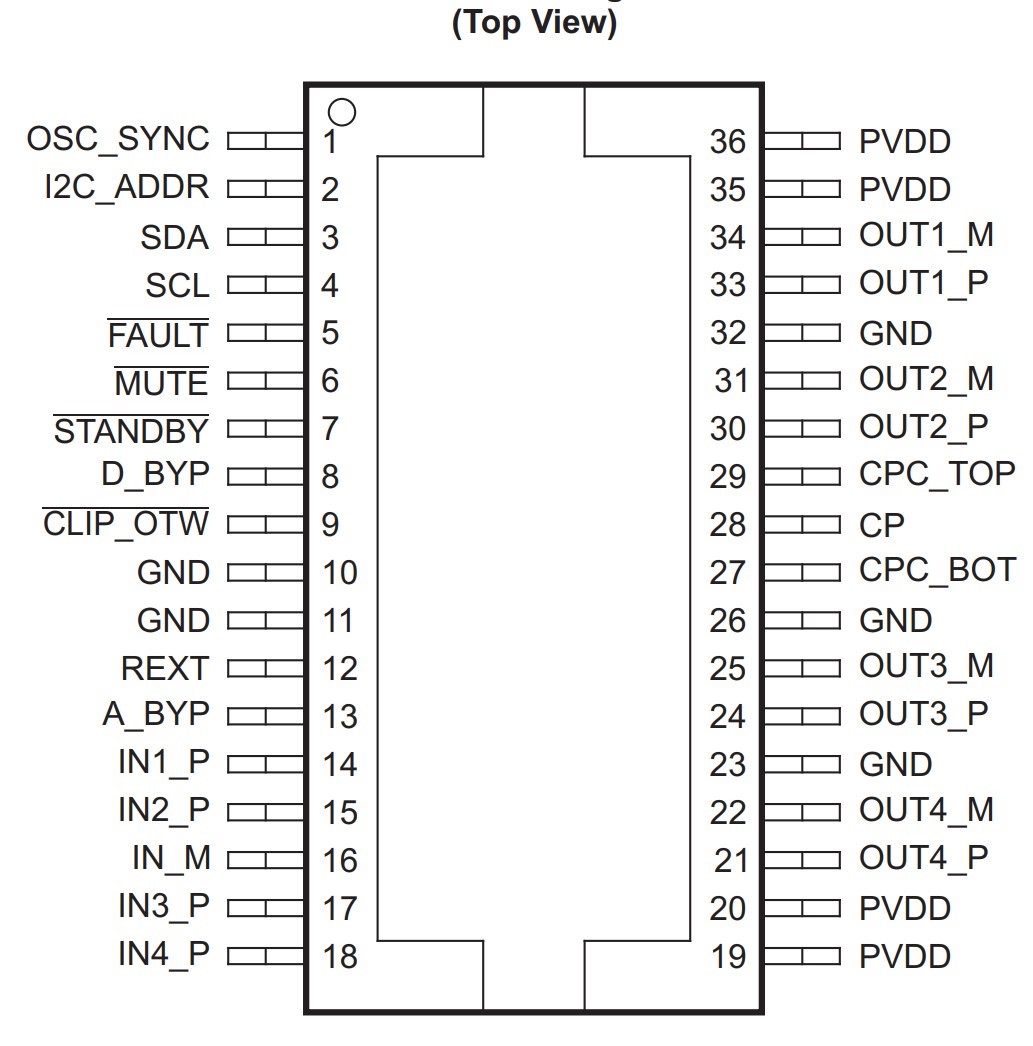

This design will work best if I place op amps in front of the TAS5414 inputs. This is a non-audio, DC-coupled application that doesn't have coupling caps at TAS54xx's inputs as suggested in the datasheet.

To do this successfully requires me to be aware of the common mode voltage range of the TAS54xx. The part's highest gain is 40 (-->32dB), so driving the outputs rail-to-rail requires about 600 mV p-p differential input voltage.

The datasheet implies that the internal DC bias point is ~3.3VDC with a common mode range of 1800mV peak to peak centered around 3.3VDC. I interpret that to mean the common mode range spans 2.4-4.2VDC for zero differential input voltage.

Does this mean that I could force onto the IN_M common bias pin a voltage of, say, 4.0VDC and still be able to drive the class D outputs rail-to-rail without distortion? Could I bias the IN-M pin any higher than 4V?

Assuming that I remain within the part's common mode range, is there any problem with forcing 4V onto the IN_M pin?

Alternatively, if I can get comfortable with letting the part self-bias its inputs at 3.3VDC, can I "sample" this internal bias voltage with an op amp and use that voltage to bias my external op amp?

The datasheet hints that the internal bias points are established with 85k resistors. Thinking aloud, this means that sampling the bias voltage with an op amp exhibiting 1nA of bias current will "pull" the TAS54xx's bias point by 85 microvolts, correct?

Thanks in advance for your feedback on this topic.

Jim Olson

Indianapolis, IN US