Hi,

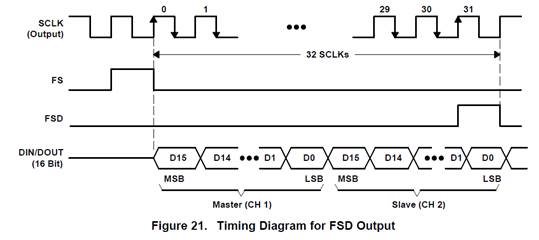

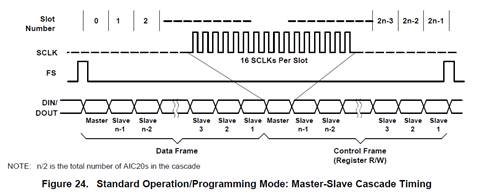

We are using three TLV320AIC24KIPFBG4 in cascaded mode in master slave configuration along with an FPGA.

The FPGA configures all three codecs and the first codec in the chain is the master.

The following is the requirement for codec configuration,

MCLK = 4.096 MHz

FS = 8 kHz

M = 4

N = 1

P = 8

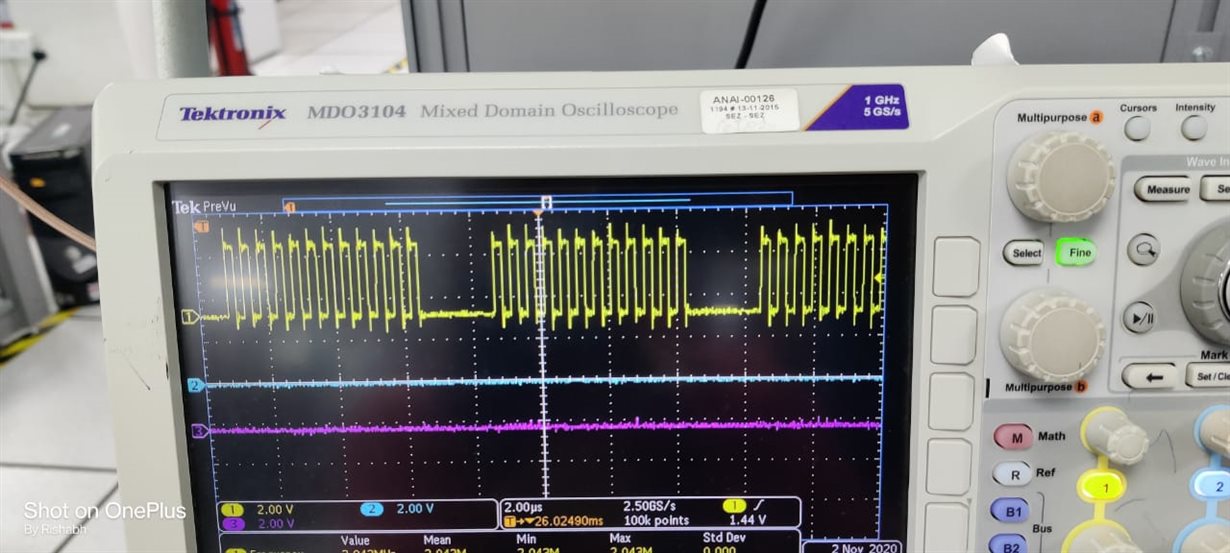

We are expecting SCLK to be 1.536 MHz based on three codec configuration.

After power up, ACD determines three codecs correctly. But once software configures the codec, we are getting SCLK as 2.048MHz which implies four cascaded codecs.

Please confirm if our understanding on SCLK frequency is correct.

Need your urgent help in this regard.

Regards,

Archana Rao