Hi, Support Team

Currently during a PR event, 48 units were produced, but two units have different AUDIO LEVEL measurements.

Circuit condition: P-LIMIT MAX, 36dB GAIN

Operating conditions: 1KHz SINE WAVE PLAY, AMP input level (RMS: 42mV)

- 46 units: 1.5V output

- 2 units: 1.9V output

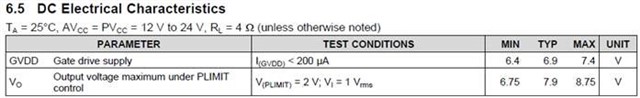

For the above reasons, GVDD, GAIN, and P-LIMIT are measured as follows.

|

|

PR일반품 |

PR이상품 |

|

GVDD |

6.94V |

6.75V |

|

P_LIMIT |

6.94V |

6.75V |

|

GAIN |

2.65V |

2.59V |

As above, we are examining the reason why some products have low GVDD output.

Currently, GVDD is used only for GAIN and P-LIMIT settings.

In addition, the resistance value is set according to TI's guide, but the GVDD voltage is low on some products.

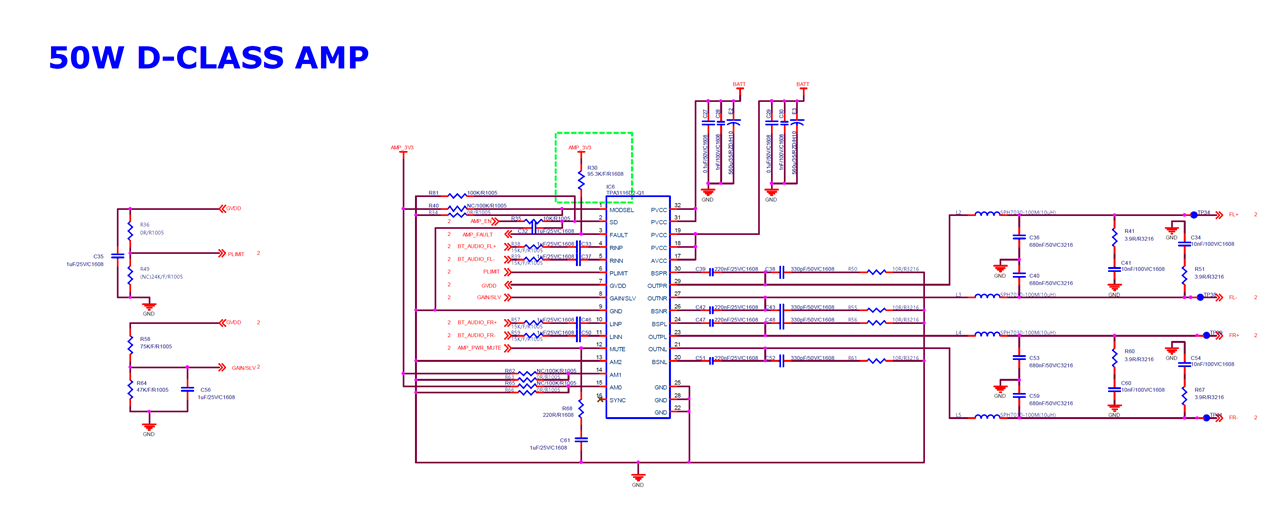

Please review the circuit configuration and capacity value by sending the circuit diagram below.

Thanks.

Regards,

MJ