HI,

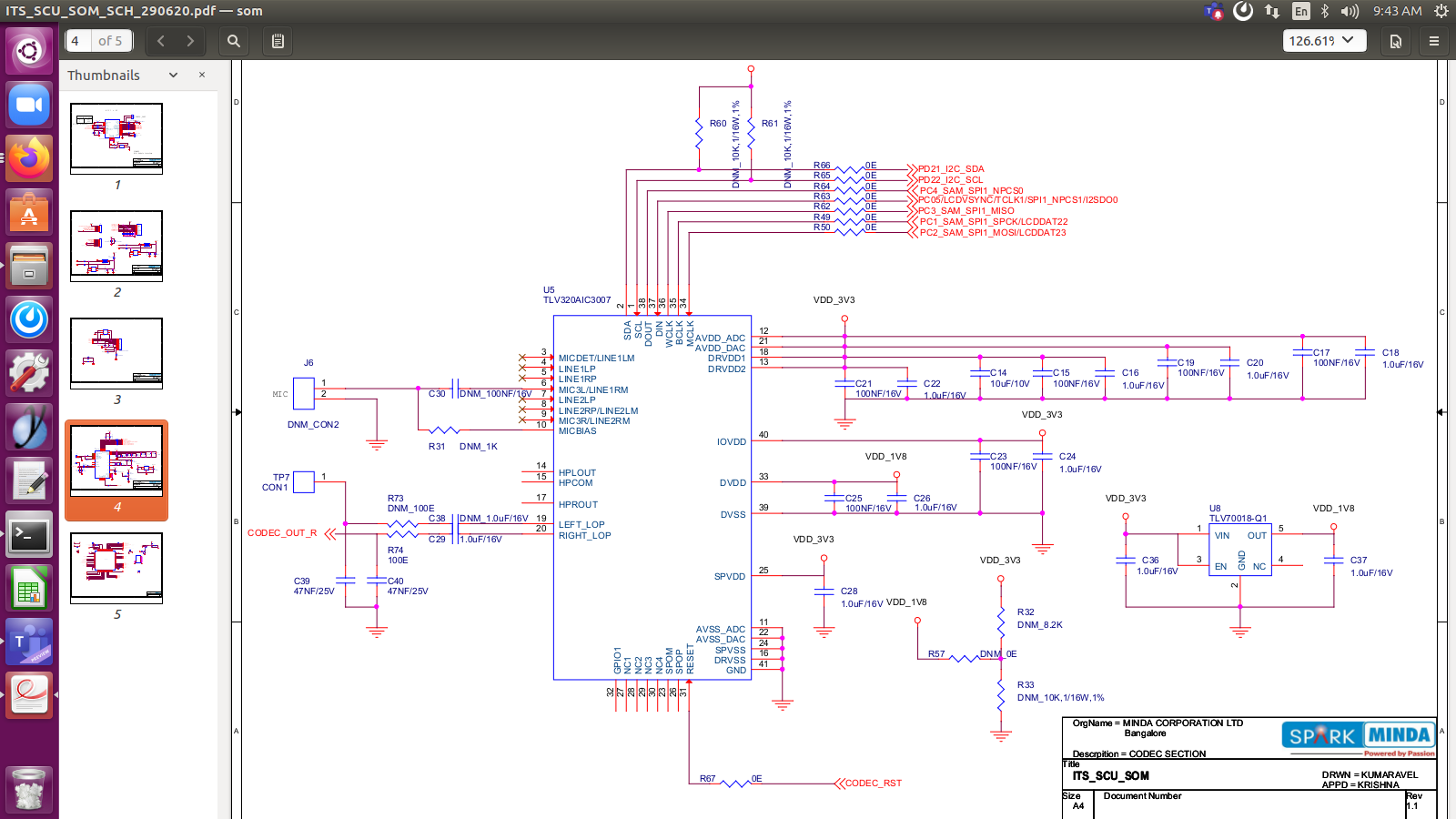

I am interfacing tlv320aic3007 codec on my carrier board,here codec working as slave mode.In slave mode audio is not working but if i use in master mode audio is working.Please have a look on below details.

1)when we are playing audio file with 16000hz sampling rate i am getting below clocks in both mode.

Codec master mode:

With below clocks audio is working in master mode.

Audio file sampling rate -16000 hz

MCLK - 12 MHz

BCLk - 512KHZ

WCLK - 16 KHz

Codec slave mode:

With below clocks audio is not working.

Audio sampling rate - 16000 hz

MCLK -12.2 MHZ

BCLK - 512 KHZ

WCLK - 15.9 khz

We are getting below dump data for both master and slave modes

root@rugged-board-a5d2x-sd1:~# i2cdump -f -y 0 0x18

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 00 00 aa 91 c0 00 00 0a 00 00 00 01 00 00 00 20 ..???..?...?...

10: 20 ff ff 00 78 78 00 78 78 02 00 fe 00 00 fe 00 ...xx.xx?.?..?.

20: 00 00 00 00 20 c0 00 00 40 40 00 00 00 2f 2f b1 .... ?..@@...//?

30: 00 00 00 0f 2f 2f af 00 00 00 0f 00 00 00 2f 2f ...?//?...?...//

40: b1 0f 00 00 00 2f 2f af 0f f4 00 00 00 00 00 00 ??...//???......

50: 2f 2f 80 00 00 00 0b 00 00 00 2f 2f 80 0b de 0c //?...?...//????

60: 00 02 00 00 00 00 02 00 00 00 00 00 00 00 00 00 .?....?.........

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 aa 91 c0 00 00 0a 00 00 00 01 00 00 00 20 ..???..?...?...

90: 20 ff ff 00 78 78 00 78 78 02 00 fe 00 00 fe 00 ...xx.xx?.?..?.

a0: 00 00 00 00 20 c0 00 00 40 40 00 00 00 2f 2f b1 .... ?..@@...//?

b0: 00 00 00 0f 2f 2f af 00 00 00 0f 00 00 00 2f 2f ...?//?...?...//

c0: b1 0f 00 00 00 2f 2f af 0f f4 00 00 00 00 00 00 ??...//???......

d0: 2f 2f 80 00 00 00 0b 00 00 00 2f 2f 80 0b de 0c //?...?...//????

e0: 00 02 00 00 00 00 02 00 00 00 00 00 00 00 00 00 .?....?.........

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

Thanks,

Prasanth