Dear TI support team,

here is an issue with the Charge Pump Voltage Monitor of the LMX2492.

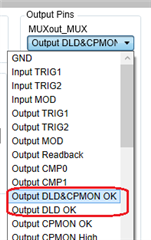

Our design had used the CPMON functionality for lock detection by assigning the "CPMON good" signal to the TRIG2 output. This has always worked reliably and without issues (series production since 2019).

Now with a design change the "CPMON good" signal doesn't go high.

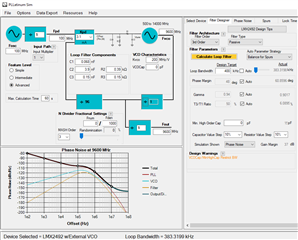

Basically, the design has not changed much (higher Q factor of the VCO, and 1 nF instead of 22 nF as first Cap to GND in the loop filter at CPout)

Settings:

Vcp: 5 V

CPM_THR_LOW: 1 V

CPM_THR_HIGH: 4 V

We see a safe lock condition on our spectrum analyzer and measure clean 2.3 V at CPout.

However, in this situation, "CPMON good" stays low, and "CPMON too low" is high.

Any ideas what this could be related to?

Thanks!