Hello,

We're observing some odd behaviour with the CDCLVP1204 during input switch over. Our system is as follows:

- Both inputs are 156.25MHz

- Both inputs are AC coupled (with 100nF caps) LVPECL signals and terminated with 50 Ohm resistors connected to the VAC_REF pin.

- Each set of 50Ohm resistors has a 0.1uF capacitor connected VAC_REF to GND.

- The LVPECL output is terminated with 150Ohm resistors on each line to GND.

- There is a 4.75KOhm pull-down resistor between IN_SEL and GND.

- VCC = 3.3V

Note: We know that the input mux is not hitless, nor do we expect it to be.

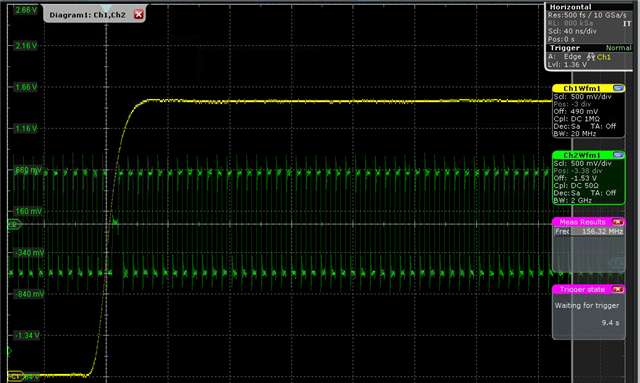

When switching from Input 0 to Input 1, the switchover occurs in <10ns and the general "shape" of the switch over is as expected. The yellow trace represents IN_SEL. The green trace is the LVPECL output from the CDCLVP1204.

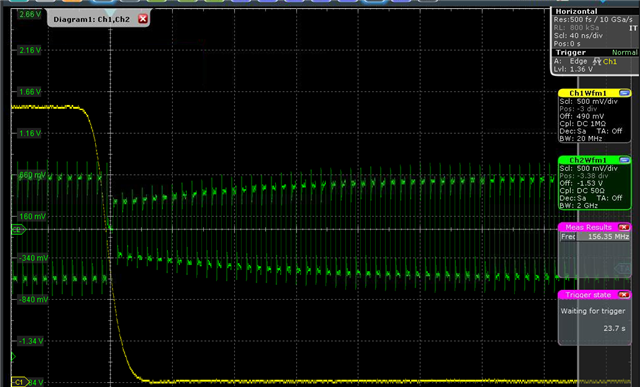

However, when switching from Input 1 to Input 0, the output is not as expected:

We see the differential output voltage droop considerably, and then "slowly" increase in magnitude to the desired steady-state value over approximately 200ns.

Some questions:

- Is this expected behaviour?

- What is the guaranteed maximum time before the outputs become stable after a switch-over?

Don