- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello!

I need someone to help me to check my design of the CDCLVD1208 clock buffer.

1) Input clock is 100MHz LVDS diff clock type,

2) Fanout 8 channels LVDS output clock, i use 7 channels LVDS output clock, (5 channels LVDS clock type, 2 channel LVPECL clock type)

3) My questions:

We ref TI some docs to add the pullup resisters to VCC, and add pulldown resisters to GND, convert the LVDS clock type to LVPECL type;

How can i choose the value of the pulldown and pullup resisters and the VCC ?

Hello,

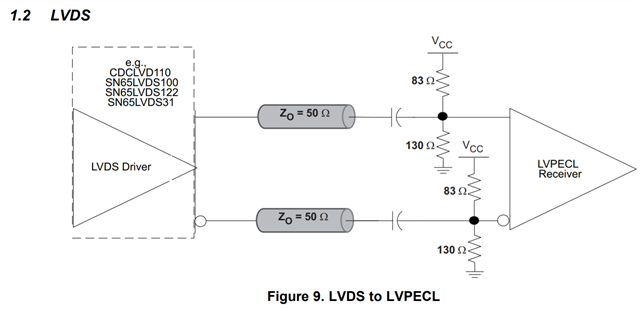

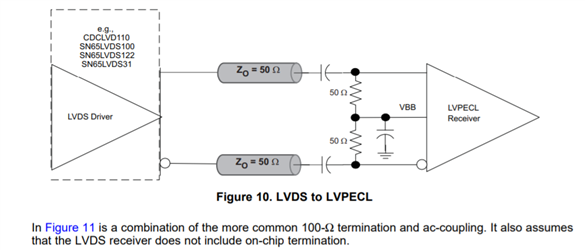

We recommend using the following configuration for Vcc = 3.3V (figure from this apps note). This is the resistor combination we typically suggest though you may confirm by simulating with the IBIS model.

Regards,

Jennifer

In the recommended circuit, Zo is 50 ohm impedance. Is it feasible if we use 100 ohm differential impedance control?

The recommended value of VCC is 3.3V, and the working voltage of cdclvd1208 is 2.5V. What is the impact here?

Hi,

You may use 100 ohm across the outputs. VCC = 2.5V may be used.

Regards,

Jennifer