Other Parts Discussed in Thread: LMX2820, LMK04828

Hi Team,

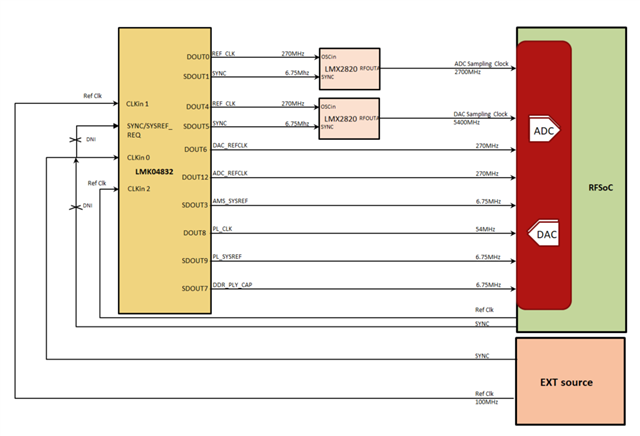

we are using LMK04832 in our design and i have few quries regarding Clkin0 as SYNC input.

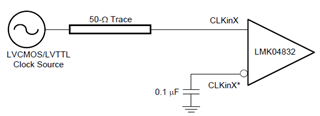

If we are using Clkin0 as SYNC input, whether it should be a single ended or differential.?

If it can be of both type, How it should be connected to LMK04832 if it is single ended or if it is diiferential?

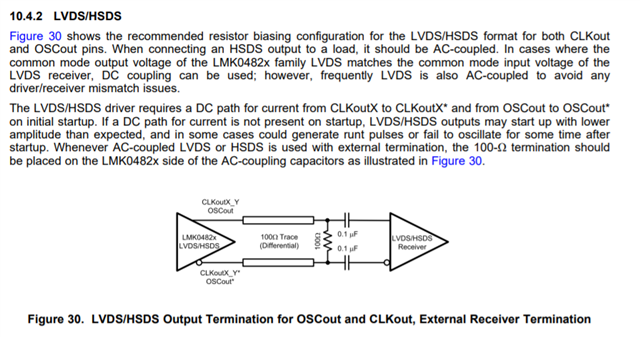

Suggest me if any ac coupling or terminations required for both the cases.

--

Thanks in Advance,

Kiran