Other Parts Discussed in Thread: LMK05318

Hello TI,

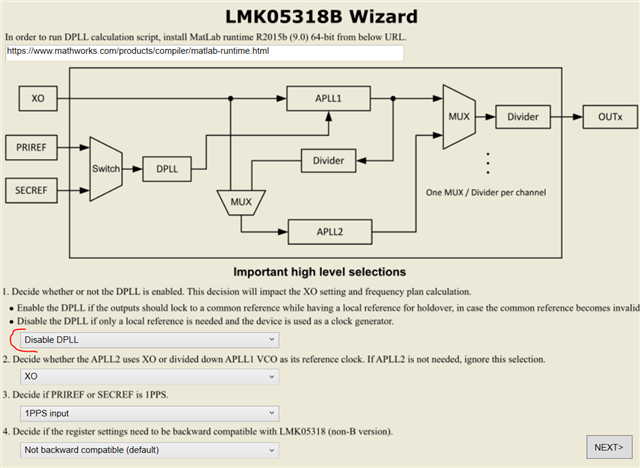

we are facing several issues with LMK05318B.

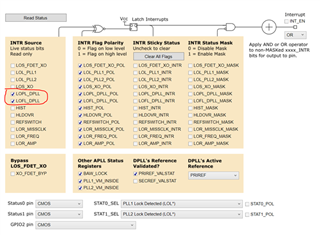

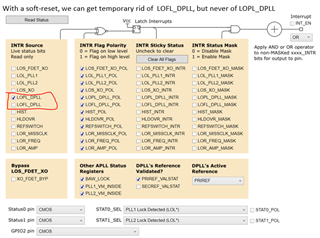

1) We're not able to get rid of two error flags of DPLL: LOFL_DPLL and LOPL_DPLL.

When the PLL is reprogrammed while run-time, LOFL_DPLL disappears, but LOPL_DPLL is always flagged.

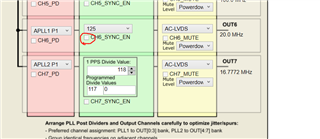

2) After boot-up, OUT7 is never up. Reprogramming the PLL at run-time enables OUT-7.

Attached is our current configuration file. Would be nice, if TI could check this configuration and guide us in solving the issues.

Thanks in advance!

LMK05318_sync TDC BW 100Hz.tcs