Hi,

We use the LMK04828 in our new project and we have the below issue for this device:

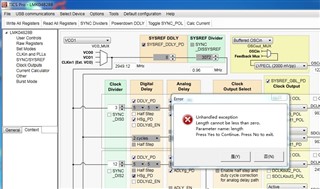

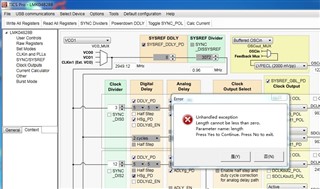

1. We use the TICS pro to set the LMK04828, and the error as below:

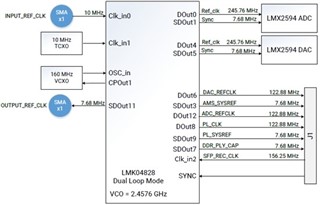

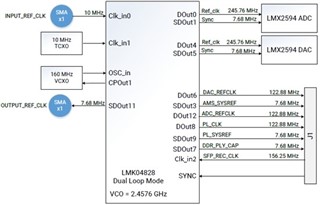

2. Please advise how to set below CLK, thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

We use the LMK04828 in our new project and we have the below issue for this device:

1. We use the TICS pro to set the LMK04828, and the error as below:

2. Please advise how to set below CLK, thanks.

Zhang,

It's not clear to me what you've done to generate this exception. Was there a specific control you interacted with to trigger this error? Can you describe the steps you took to generate this error?

Can you navigate to C:\Program Files (x86)\Texas Instruments\TICS Pro, and share the ErrorLog00.txt file and log00.txt/log01.txt files if present?

Regards,

Derek Payne

Hi Derek,

Attach for your evaluating, thanks.

TICS Pro.exe Warning: 0 : 04/08/2022 10:52:34 Unhandled exception 长度不能小于 0。 参数名: length ----------------------------------

Welcome to TICS Pro. Version -> 1.7.4.1, 10-Feb-22 Loading Device LMK04828B... Detected 0 USB2ANY interfaces Completed loading Device LMK04828B. Version = 2019-06-12, v4.0.0, scripts=fa67100541

Zhang,

I've identified three places in the code that could be raising the error you describe:

Which of these were you attempting?

---

I've reviewed your configuration request, and I have a few comments before we proceed:

Regards,

Derek Payne

Hi Derek,

The error is the load a configruration, and we choose the File ----> load ----- LMK04828, and the error show as the attach;

For the section 2, we will test first and many thanks for your kindly support

Hi Derek,

For the section 2, pleaes refe to below reply: