Part Number: LMK5B12204

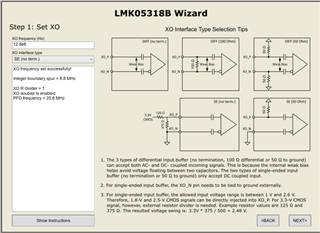

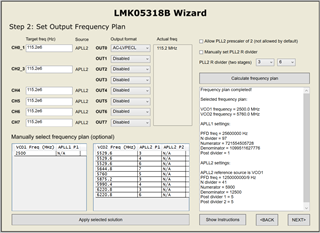

Other Parts Discussed in Thread: LMK05318B

Hello,

I have a quick question about the reference input.

I am testing the tracking or SYNC feature in the LMK05318B EVM with the reference input, but it does not work properly as I expect.

With 96MHz sine wave signal to PRIREF input as a reference, I could not get the output frequency shift according to the frequency shift of reference 96MHz.

Can you tell me that my understanding on this is right?

Thank you.