Other Parts Discussed in Thread: LMK05318B, CDCE6214, CDCI6214, LMK05318, CDCE937, CDCM6208

Hi,

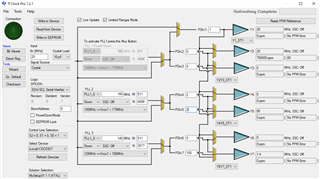

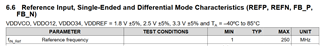

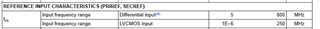

i am using LMK03328 right now to generate multi clocks for my system. i wish to generate one more 1.4MHz clock. But i failed to configurate it in TICS Pro. I saw the LMK03328 programming tutoiral. But i still cannot generate 1.4MHz clock. the minim clock i can do is 2.3MHz. The datasheet show the minim VCO output is 4800MHz, the maxim out devider is 8 and 256. so the minim output frequency is 4800/8/256=2.34375MHz. This is the minim freqeucy i can get withou error in the software. Why the datasheet show the minim output is 1MHz. How could i do it? Even i make the output from refence input dierectly, it still failed if make the input is 1.4MHz..

Thanks,

Shu