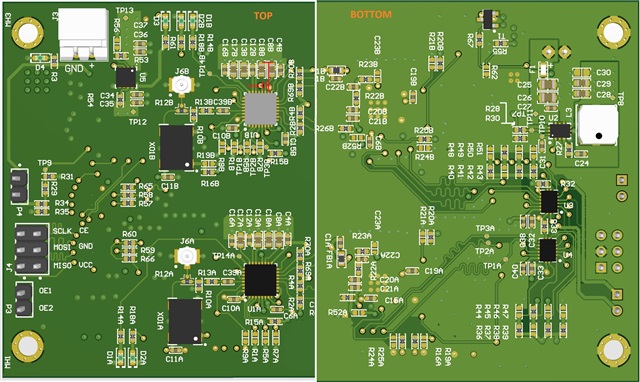

I was given a certain project to lead. It was carried out by a person who is no longer with us and I have a problem finishing it.

On the developed board there are 2 pieces of LMX2581. I managed to run the power supply (stable 3.28V) and establish communication with the circuits. HOWEVER, the output frequencies are incorrect. Is equal than 3.8 GHz (VCO mode) or less than set(channel divider mode). I checked the input frequency, it is correct and equal to 100 Mhz, for both my circuits.

n addition, I replaced the loop original filter values with those suggested by Clock Design Tool:

I include screenshots of the settings and the resulting values:

R15 0x021FEA0F R13 0x4080410D R10 0x210050CA R9 0x03C7C039 R8 0x207DDBF8 R7 0x00082317 R6 0x000004C6 R5 0x00308005 R4 0x00000004 R3 0x2000F3C3 R2 0x0C000012 R1 0xC0000081 R0 0x60A00000