Hi,

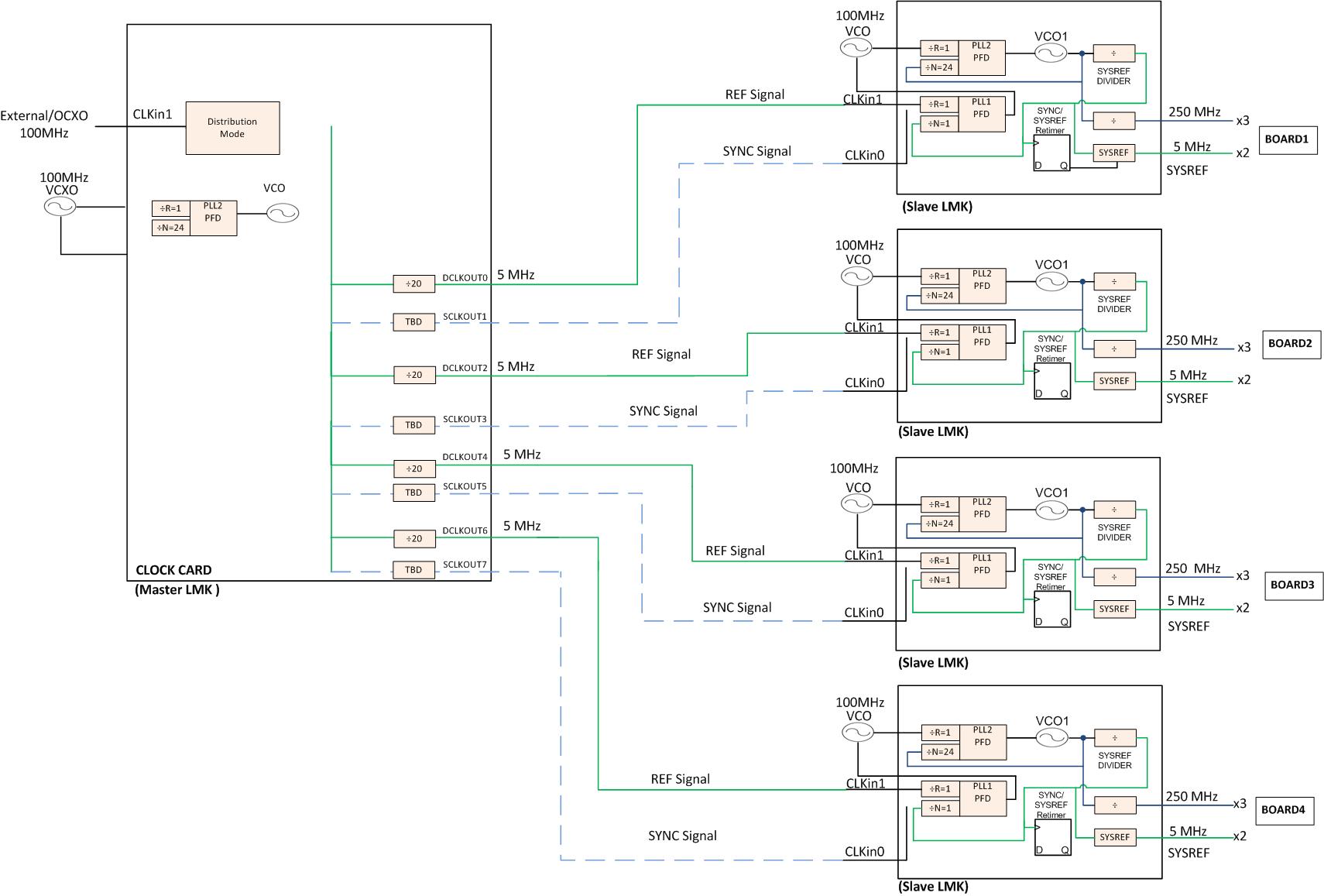

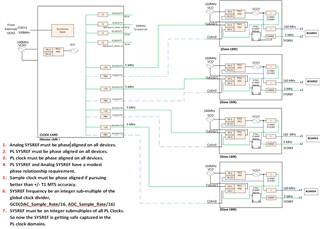

We are planning to use LMK04828 Clock Synthesizer(Master and Slave scheme) to RFSoC FPGA multi-board synchronization.

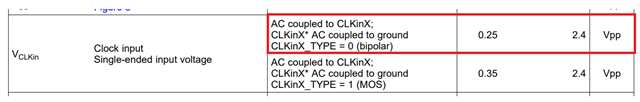

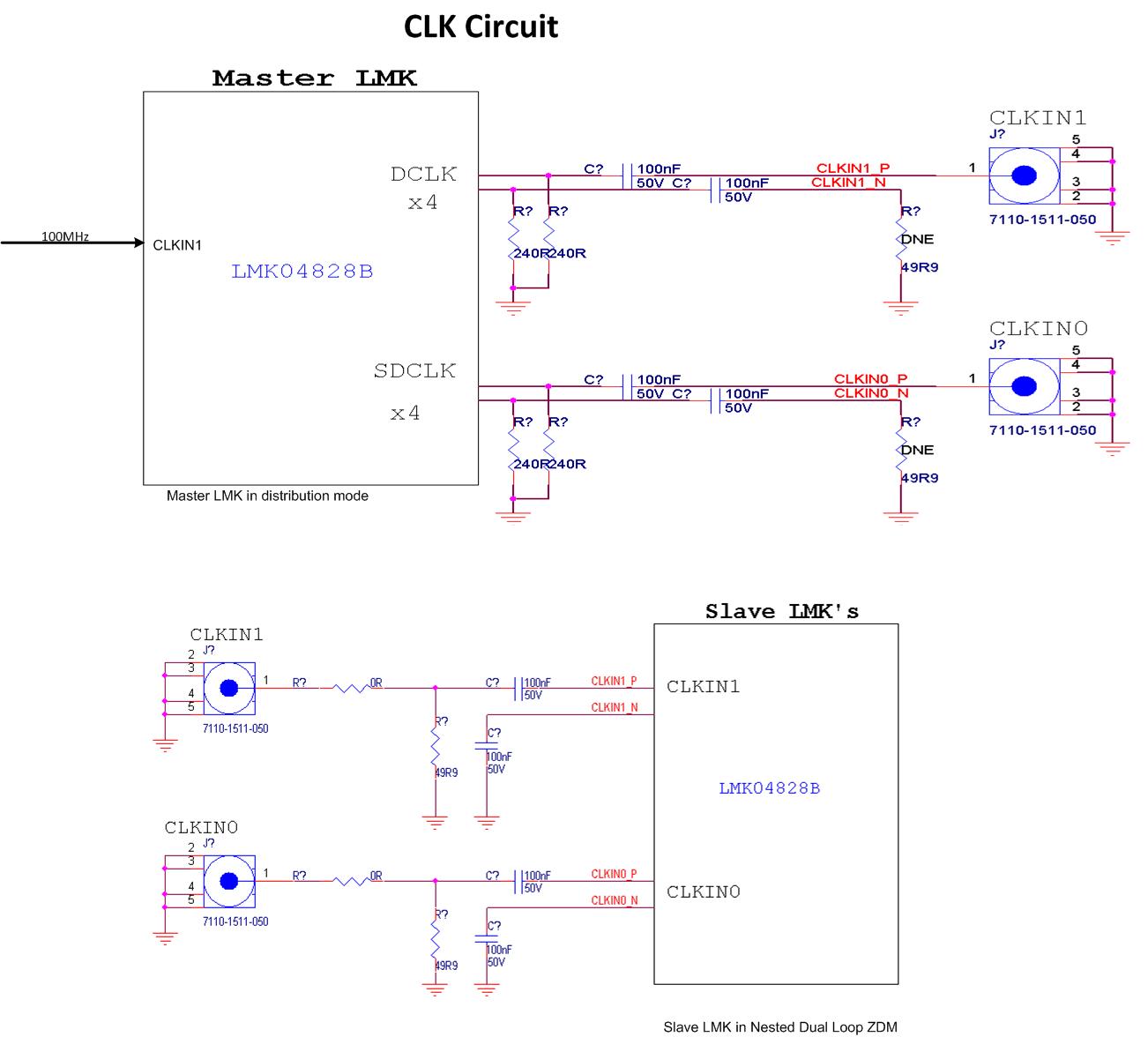

- The Master LMK will have reference clock of 100MHz at CLKIN1 from external/on board OCXO(optional).

- The Master LMK will be in distribution mode, and generating 5MHz of reference clock for the Slave LMK's.

- All the slave LMK's will receive reference clock of 5MHz at CLKIN0 from Master LMK& will be through matched cables.

- All the Slave LMK's will have 160MHz VCXO input to OSCIN

- Slave LMK's will be generating 160MHz DCLKOUT and 5MHz SYSREF to follow the ZDM and in Dual loop mode.

- All 4 slave LMK output clocks need to be synchronized and aligned for Multi-clock synchronization.

Please verify the below scheme and confirm that All the slave LMK will have deterministic latency from power on to power on.

We will share configuration files.

.

.