Hi team,

One of our customer's issues, I'm forwarding it below, could you please provide some troubleshooting suggestions

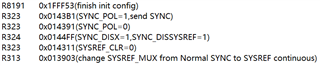

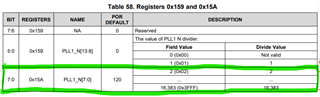

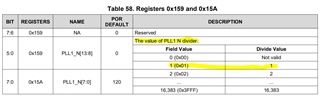

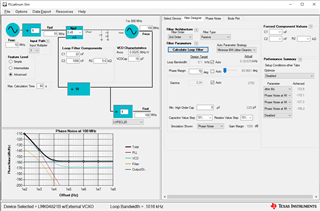

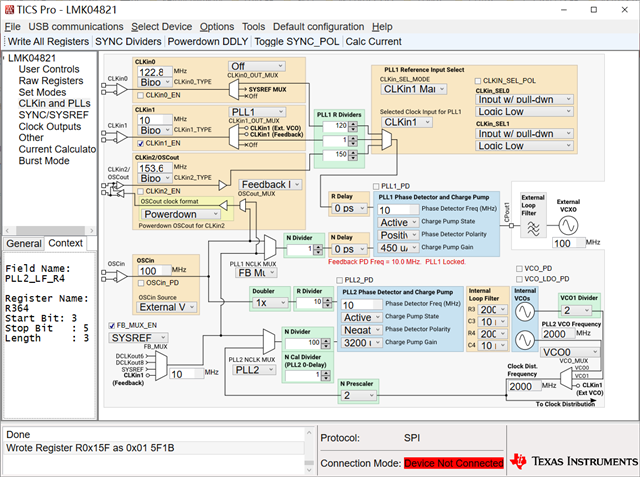

Using lmk04821, works in Dual-pll cascaded zero-delay mode, the TICS pro configuration file is lmk04821_config.tcs.The reference clock input is a 10MHz, 5dBm sine wave, input from CLKin1.Grab the PLL_DLD signal from the chip IO output via the FPGA. PLL1 was found to be occasionally out of lock, after which it was about 0.16ms then locked again; PLL2 was always locked. May I know what is the probable cause of the PLL1 being out of lock and if it is not configured in the correct way.

Best Regards,

Amy Luo