Hello Team,

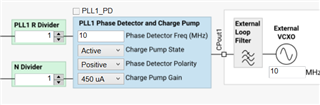

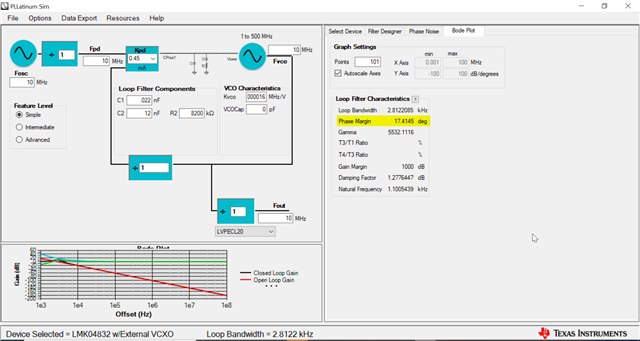

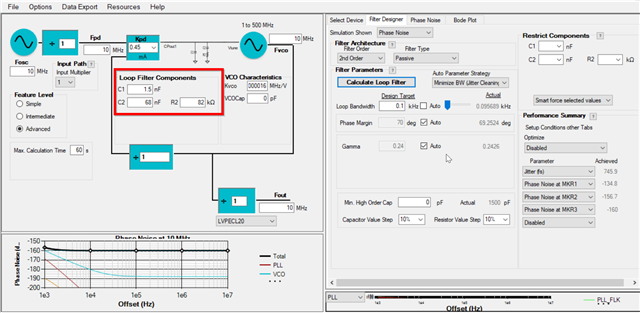

We are attempting to use a VCOCXO as the External VCXO reference for our dual loop PLL; however, we cannot get a lock with our current design.

The 10MHz VCOCXO we are using has a control voltage range of 0-5V resulting in a +/-4Hz deviation. We have designed an amplifier to take the 3.3V output of the LMK04832 to drive the 0-5V requirement of the VCOCXO.

Is there something we are missing in configuration or loop-back filter that would result in the PLL never locking?

I have attached our TICS configuration & loop-back filter simulation.

Thanks,

Grant