Other Parts Discussed in Thread: , USB2ANY

Hi, TI expert,

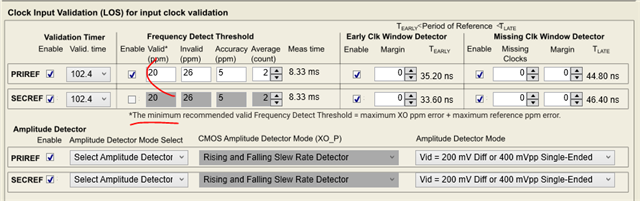

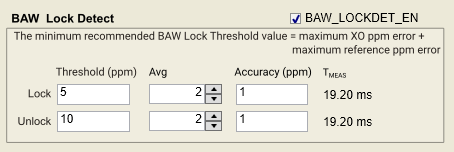

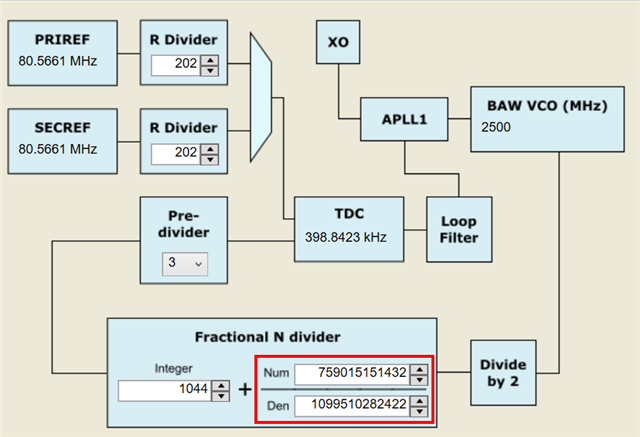

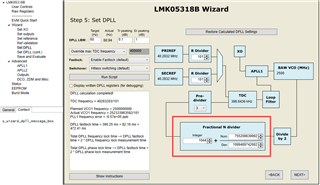

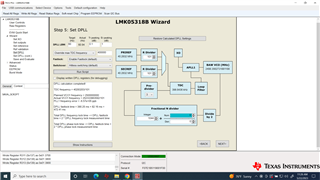

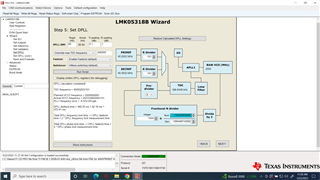

I am using LMK05318 on my board. I have 20ppm frequence deviation for DPLL Primary and Secondary Reference Clock Inputs (PRIREF_P PRIREF_N, SECREF_P SECREF_N).

For example, in my test:

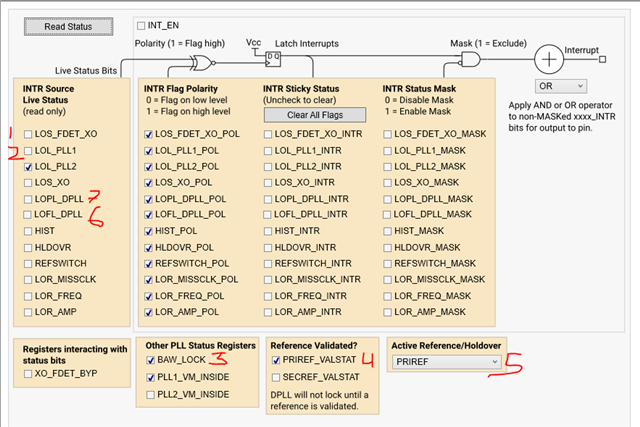

80566140 Hz input via TICS Pro software makes LMK05318 DPLL lock.

80566406 Hz via TICS Pro software does NOT make LMK05318 DPLL lock(LOFL_DPLL=1), even other settings are the same.

80566140 Hz is from our real measurement on one board. 80566406 Hz is from our calculation.

What is the frequence deviation tolerance (? ppm) for DPLL Primary and Secondary Reference Clock Inputs? Thanks!

I cannot measure every board to determine the accurate frequence for DPLL Primary and Secondary Reference Clock Inputs.

Other condition in my test :

XO: 48MHz input with 25ppm. Use LMK05318 DPLL and APLL1, not use APLL2.

Thanks!

Vaison