- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

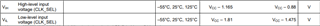

The datasheet specifies CLK_SEL VIH/VIL Spec as follows.

However, looking at CDCLVP111-SP Evaluation Module schematics, CLK_SEL VIH/VIL could be VCC or VEE exceeding the VIH/VIL Spec in the datasheet.

Which is wrong, datasheet or EVM?

Best regards,

K.Hirano

Hi Kazuhiko,

We need to look at the actual VIH and VIL data for this part to confirm this with you. We would be able to respond on this by next week.

Best,

Asim

Asim,

Thank you for taking care of my question.

I look forward to receiving your answer next week.

Best regards,

K.Hirano

Asim,

How is it going?

Please let me know around when you think you would be able to respond.

Best regards,

K.Hirano

Hi Kazuhiko, apologies for the delay. I'll take care of you as Asim is out of office. I contacted the design team and will keep you updated.

Regards,

Juan

Hi Kazuhiko,

I will have a response to you tomorrow. Thank you for your patience!

Regards,

Juan

Hi Kazuhiko,

Keep in mind that there is no ground pin on the CDCLVP111-SP. I believe that the way this EVM is being powered is where the confusion lies. At first glance, it seems as if VEE is 2 V, which it is not, it is the negative pin on the 3.3 V supply (as shown in the image below). The image also shows the supply configuration table for what the VCC:VEE spec should be.

This brings me to my next point. If you take a close look at the EVM schematic, the jumper is providing a connection to the input of the CLK_SEL pin, but that is not the supply that is being selected with the jumper. The jumper offers you a way to short the input pin to the buffer's local supply or local ground. You can view VEE as the "local ground" in LVPECL operation in this case. VEE is available for you in the case you want to operate LVECL conditions.

To answer your question, both the datasheet and the EVM are correct. Please ensure that you follow the LVPECL voltage requirements on the datasheet.

Regards,

Juan

Juan,

Thank you for your responses.

However, I still have questions.

I see VCC=2V and VEE=-1.3V at the EVM.

And, CLK_SEL input could be either 2V(VCC) or -1.3V(VEE) on the EVM depending on J1 setting.

However, according to the datasheet VIH/VIL spec for CLK_SEL, VIH on the EVM has to be VCC-1.65(2-1.165=0.835V) to VCC-1.125 (2-1.125=0.875V) and VIL on the EVM has to be VCC-1.81(2-1.81=0.19V) to VCC-1.475 (2-1.475=0.525V). So, CLK_SEL high/low on the EVM (2V/-1.3V) is out of spec. I do not think the EVM is correct.

Actually, if the datasheet spec is true, customers are complaining that they have to have different specific voltage rail from VCC or VEE to control only CLK_SEL.

If you could provide further comments on this, it would be very helpful and appreciated.

Best regards,

K.Hirano

Hi Kazuhiko,

As Juan mentioned above. EVM is correct because there is no ground pin on the IC. It has VEE and VCC pin. And CLKINSEL pin is referencing these two pins for setting the threshold voltage. From EVM, VCC is set to 3.3V and VEE is set to 0V. It complies with datasheet spec.

Board ground is being used as biasing voltage for LVPECL termination scheme.

Best,

Asim

Asim,

Thank you for your response.

However, I think you do not understand my question.

Here, let me ask my question again.

You mentioned Vcc=3.3V and Vee=0V at EVM.

OK then, let’s take a look at the datasheet 6.6 LVPECL DC Electrical Characteristics.

VIH(max) for CLK_SEL is VCC – 0.88 = 3.3 – 0.88 = 2.42V. However, if J1-2 and J1-3 are connected, CLK_SEL gets VCC (3.3V) and it is above VIH(max) = 2.42V specified in datasheet.

VIL(min) for CLK_SEL is VCC – 1.81 = 3.3 – 1.81 = 1.49V. However, if J1-2 and J1-1 are connected, CLK_SEL gets VEE (0V) and it is below VIH(min) = 1.49V specified in datasheet.

So, both CLK_SEL high and low are out of spec on the EVM.

Which is wrong, datasheet CLK_SEL VIH(max)/VIL(min) spec or EVM settings?

Best regards,

K.Hirano

Hi Kazuhiko,

It seems like their is a misunderstanding with how the spec is written in the datasheet. This specification is for comparator threshold voltage variation region. Max spec specify that if the CLK_SEL level is higher than that then it would switch to high and min specification specification tells us for minimum voltage needed for comparator to detect high.

VIH(max) for CLK_SEL is VCC – 0.88 = 3.3 – 0.88 = 2.42V. However, if J1-2 and J1-3 are connected, CLK_SEL gets VCC (3.3V) and it is above VIH(max) = 2.42V specified in datasheet.

For setting CLK_SEL in high state you need to apply higher voltage then 2.42 or equal to this value. So applying VCC which higher than VIH threshold should be okay and give you correct state for CLK_SEL.

VIL(min) for CLK_SEL is VCC – 1.81 = 3.3 – 1.81 = 1.49V. However, if J1-2 and J1-1 are connected, CLK_SEL gets VEE (0V) and it is below VIH(min) = 1.49V specified in datasheet.

Same thing goes here. When you have CLK_SEL voltage below VCC - 1.81 then it would detect and VCC - 1.475 tells us the maximum voltage level that we need to apply for comparator to detect low.

Best,

Asim

Asim,

Thank you for your detailed explanations.

Now I understood what the datasheet specifies here.

However, this VIH/VIL spec is different from usual and I hope the datasheet would be revised next timing so that it specifies only VIH(min) and VIL(max) as the same as most other datasheet to avoid confusions. Customer do not think the spec is for threshold window usually.

Best regards,

K.Hirano

Hi Kazuhiko,

We will update it to reflect the commonly used terminology as other devices.

Best,

Asim