Other Parts Discussed in Thread: , LMX2820, LMX2595, LMX2594, LMX2572

Hi!

We are planning to use LMK04832 in Single loop 0-delay mode for our application which has a stringent phase noise requirement,

The configuration is as follows,

OSCin: 100MHz from Very Low Phase Noise(-130dBc @ 100Hz) OCXO of TTL Sqaure Wave

VCO1 : 3200MHz

OUT1:100MHz @ LVPECL1.6

OUT2: 1600MHz @ LVPECL1.6

OUT3: 400MHz @ LVDS

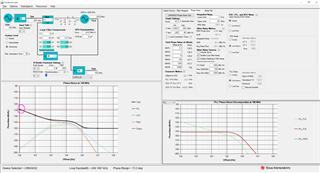

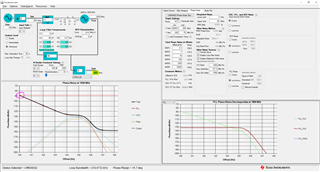

On simulating the Output 100MHz Phase noise in PLLatinum sim software, -4dB degradation in phase noise is observed at 100Hz offset as shown below,

Query:

1.Since phase noise is of utmost importance for our application, Kindly confirm if the phase noise degradation will not exceed -4dB degration i.e, -126dBc/Hz @ 100Hz offset when using LMK04832? or will practical implementation incur additional degradation?

2.Is there any better part that could provide less Phase noise degradation at lower offsets(<10KHz) and with 0-delay feature, Sysref generation?

Thanks in-advance,

Deva