Other Parts Discussed in Thread: LMK04821, LMK04828, LMK04228

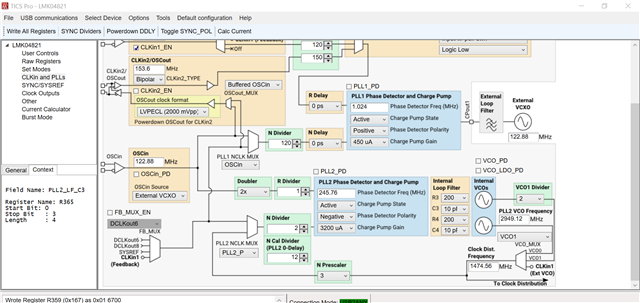

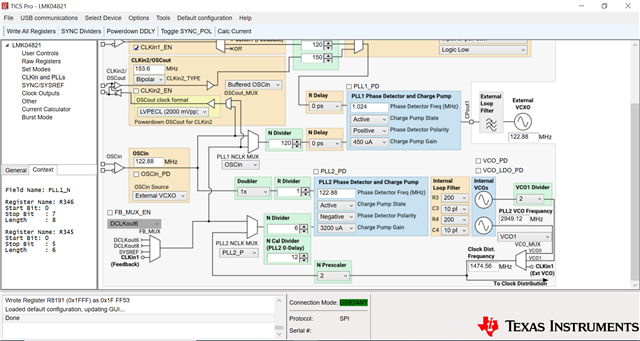

LMK04821EVM 默认配置(如图1所示)下PLL2无法锁相(Status_LD2 不亮),输出时钟频率不正确

图1:

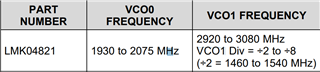

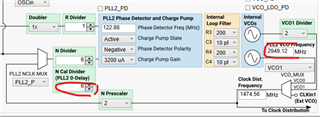

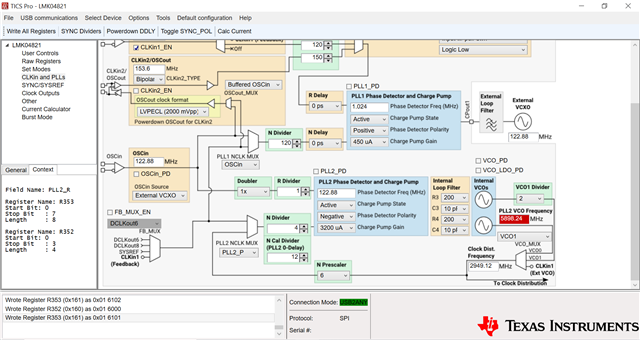

修改N Divider和N prescaler可以实现锁相(Status_LD2 亮,输出时钟频率正确可调),但VCO1 输出频率已经超出Datasheet范围,PLL2的锁相频率fpd2也不满足手册要求,配置如下图2所示:

图2:

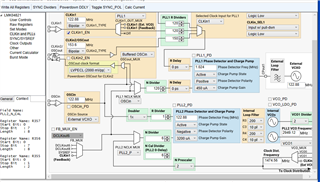

修改Doubler 和 Divider,可以在满足VCO输出频率范围的条件下锁相(Status_LD2 亮,但输出时钟频率不正确),配置如图三所示

图3: