PRIREF is recognized as valid, but the DPLL doesn't lock to the 1pps reference input signal.

Hi

I am working on a clock synchronized with a GPS signal. Then two separate boards is considered synchronized .

I have applied to the PRIREF input the 1pps signal coming from the module NEO-M8T.

I have changed XO to ECS-TXO-2520MV-120-AY-TR . It is 2.5ppm and 12MHZ .

I have read all the posts on the forum regardingLMK05138B GPSlock issues .

I use the latest TICS Pro v1.7.5.15 .

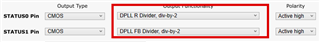

My problem is similar to this topic . When I download Q100_max_TI_working.tcs , and modify to my frequency . My tcs file is here LMK05318BRGZT_GPS_1HZ_NEO-M8N_XO12MHZ_2p5PPS_50MHZ.tcs.

I export EEPROM Sequence and write to the LMK05318B .Then pull PDN pin low .

I succesfully generate 125 MHz /100MHz / 50MHz outputs, but I cant get DPLL lock (i suppouse that chip is in free-run ).

When I read register , R411 PRIREF is valid ,but R14 LOFL, LOPL is high , DPLL is not locked . I have tried soft-reset chip (wr R12 and then clear ) and wait for minutes .

Please let me know if you need any more information.

Can you help us understand why it would not be locking and what can be done to resolve this?