Hi,

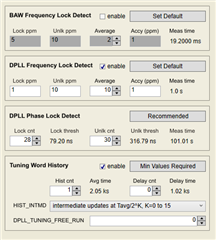

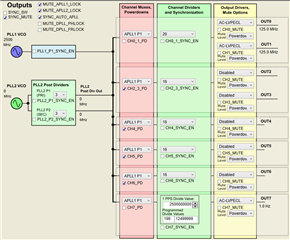

my problem is similar to this topic. I succesfully generate 125 MHz and 1 Hz outputs, but I cant get lock (i suppouse that chip is in free-run). R14 register status have LOFL, LOPL and HLDOVR flags. Register R13 is clear. I have Tics Pro from january 7 2022, i tried to use fix from this topic with same result.

Please let me know if you need any more information.

Can you help us understand why it would not be locking and what can be done to resolve this?

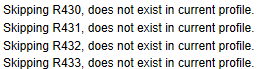

R0 0x000010 R1 0x00010B R2 0x000235 R3 0x000332 R4 0x000404 R5 0x00050E R6 0x000617 R7 0x00078E R8 0x000802 R10 0x000AC8 R11 0x000B00 R12 0x000C1B R13 0x000D08 R14 0x000E00 R15 0x000F00 R16 0x001000 R17 0x00111D R18 0x0012FF R19 0x001308 R20 0x001420 R21 0x001501 R22 0x001600 R23 0x001755 R24 0x001855 R25 0x001900 R26 0x001A00 R27 0x001B00 R28 0x001C01 R29 0x001D13 R30 0x001E40 R32 0x002044 R35 0x002300 R36 0x002403 R37 0x002500 R38 0x002600 R39 0x002702 R40 0x002803 R41 0x002900 R42 0x002A01 R43 0x002BC2 R44 0x002C01 R45 0x002D03 R46 0x002E11 R47 0x002F07 R48 0x003050 R49 0x00314A R50 0x00321E R51 0x003310 R52 0x003410 R53 0x003513 R54 0x003600 R55 0x003700 R56 0x00380F R57 0x003900 R58 0x003A0F R59 0x003B00 R60 0x003C0F R61 0x003D00 R62 0x003E63 R63 0x003F3E R64 0x004095 R65 0x004102 R66 0x0042F8 R67 0x0043FF R68 0x004408 R69 0x004500 R70 0x004600 R71 0x004700 R72 0x004833 R73 0x004900 R74 0x004A00 R75 0x004B00 R76 0x004C00 R77 0x004D0F R78 0x004E00 R79 0x004F11 R80 0x005080 R81 0x005116 R82 0x005200 R83 0x005303 R84 0x005484 R85 0x005500 R86 0x005600 R87 0x005706 R88 0x00581A R89 0x005980 R90 0x005A00 R91 0x005B18 R92 0x005C00 R93 0x005D03 R94 0x005E84 R95 0x005F00 R96 0x006000 R97 0x006106 R98 0x00621A R99 0x006380 R100 0x006429 R101 0x006501 R102 0x006622 R103 0x00670F R104 0x00681F R105 0x006905 R106 0x006A00 R107 0x006B64 R108 0x006C00 R109 0x006D53 R110 0x006E55 R111 0x006F55 R112 0x007055 R113 0x007155 R114 0x007255 R115 0x007303 R116 0x007401 R117 0x007500 R118 0x007600 R119 0x007700 R120 0x007800 R121 0x007900 R122 0x007A00 R123 0x007B28 R124 0x007C00 R125 0x007D11 R126 0x007E79 R127 0x007F7A R128 0x008000 R129 0x008101 R130 0x008200 R131 0x008301 R132 0x008401 R133 0x008577 R134 0x008600 R135 0x00872B R136 0x008800 R137 0x008928 R138 0x008AE5 R139 0x008B03 R140 0x008C02 R141 0x008D00 R142 0x008E01 R143 0x008F01 R144 0x009077 R145 0x009101 R146 0x009289 R147 0x009320 R149 0x00950D R150 0x009600 R151 0x009701 R152 0x00980D R153 0x009929 R154 0x009A24 R155 0x009B32 R156 0x009C01 R157 0x009D00 R158 0x009E00 R159 0x009F00 R160 0x00A0FC R161 0x00A132 R162 0x00A200 R164 0x00A400 R165 0x00A500 R167 0x00A701 R178 0x00B200 R180 0x00B400 R181 0x00B500 R182 0x00B600 R183 0x00B700 R184 0x00B800 R185 0x00B9F5 R186 0x00BA01 R187 0x00BB00 R188 0x00BC00 R189 0x00BD00 R190 0x00BE00 R191 0x00BF00 R192 0x00C050 R193 0x00C118 R194 0x00C218 R195 0x00C33F R196 0x00C4FF R197 0x00C5FF R198 0x00C63F R199 0x00C7FF R200 0x00C8FF R201 0x00C900 R202 0x00CA3F R203 0x00CBFF R204 0x00CCFF R205 0x00CD3F R206 0x00CEFF R207 0x00CFFF R208 0x00D000 R209 0x00D114 R210 0x00D200 R211 0x00D316 R212 0x00D400 R213 0x00D514 R214 0x00D600 R215 0x00D716 R216 0x00D800 R217 0x00D900 R218 0x00DA00 R219 0x00DB00 R220 0x00DC01 R221 0x00DD03 R222 0x00DE93 R223 0x00DF87 R224 0x00E000 R225 0x00E100 R226 0x00E200 R227 0x00E300 R228 0x00E401 R229 0x00E503 R230 0x00E693 R231 0x00E787 R232 0x00E800 R233 0x00E910 R234 0x00EA10 R235 0x00EB00 R236 0x00ECC3 R237 0x00ED50 R238 0x00EE00 R239 0x00EF00 R240 0x00F0C3 R241 0x00F150 R242 0x00F200 R243 0x00F33F R244 0x00F43F R249 0x00F921 R250 0x00FA00 R251 0x00FB02 R252 0x00FC6D R253 0x00FD00 R254 0x00FE00 R255 0x00FF00 R256 0x010000 R257 0x010101 R258 0x010200 R259 0x010301 R260 0x010402 R261 0x010580 R262 0x010601 R263 0x01072A R264 0x010805 R265 0x0109F2 R266 0x010A00 R267 0x010BA0 R268 0x010C04 R269 0x010D00 R270 0x010E03 R271 0x010FFD R272 0x01101F R273 0x01111F R274 0x01121F R275 0x01131D R276 0x01141D R277 0x01151D R278 0x011600 R279 0x011700 R280 0x011800 R281 0x011900 R282 0x011A00 R283 0x011B00 R284 0x011C1E R285 0x011D1E R286 0x011E00 R287 0x011F00 R288 0x012000 R289 0x012100 R290 0x012202 R291 0x012389 R292 0x012409 R293 0x012501 R294 0x012600 R295 0x01272C R296 0x012805 R297 0x012905 R298 0x012A05 R299 0x012B01 R300 0x012C00 R301 0x012D15 R302 0x012E17 R303 0x012F01 R304 0x01300F R305 0x013104 R306 0x013261 R307 0x0133F8 R308 0x013443 R309 0x0135C3 R310 0x0136C3 R311 0x0137C3 R312 0x0138C3 R313 0x0139C3 R314 0x013AFF R315 0x013BFF R316 0x013CFF R317 0x013DFF R318 0x013EFF R319 0x013F03 R320 0x014000 R321 0x01410A R322 0x014200 R323 0x014300 R324 0x014400 R325 0x014501 R326 0x014606 R327 0x014735 R328 0x014875 R329 0x01490B R330 0x014A00 R331 0x014B64 R332 0x014C00 R333 0x014D00 R334 0x014E00 R335 0x014F01 R336 0x015006 R337 0x015135 R338 0x015275 R339 0x01530B R340 0x015400 R341 0x015500 R342 0x015600 R343 0x015700 R344 0x015800 R345 0x015900 R346 0x015A02 R347 0x015B00 R348 0x015C00 R349 0x015D00 R350 0x015E00 R351 0x015F00 R352 0x016000 R357 0x016528 R367 0x016F00 R411 0x019B08