Other Parts Discussed in Thread: LMX2581

Hello, this is a follow-up question to this:

https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1278540/trf3765-getting-phase-coherent-behavior-of-multiple-frequencies-out-of-trf3765/4857650

We're using multiple LMX2572 PLLs, that we want to have phase-coherent to each other, but also to a reference frequency (e.g. the input frequency of PLL), that all are phase-aligned to the zero-phase point of the PLL.

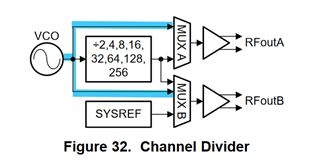

The desired operating frequency is the ISM Band between 2.4 GHz and 2.5 GHz. Unforunatly, this wasn't doable without a channel divider. As stated in the datasheet (page 17/90):

"To go below the VCO lower bound of 3.2 GHz, the channel divider can be used". Ideally, we would like to bypass this, since we only want to use an integer PLL (e.g. 100MHz * (N = 24) = 2,4GHz)

Question 1: Is there a way to get this without the Channel Divider, that we're missing in the datasheet?

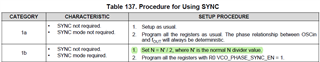

As suggested by the datasheet (page 67/90):

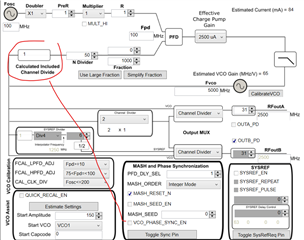

Red path: We set CHDIV = 0 (Which gives a channel divider value of 2 for the equation)

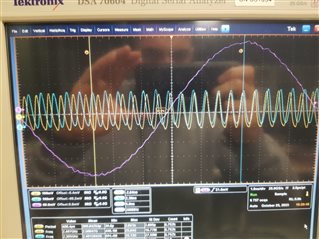

1. (PLL_N = 50, PLL_NUM = 0 & PLL_DEN = 1000) to result (2,5GHz) --> Channel 1 (Yellow)

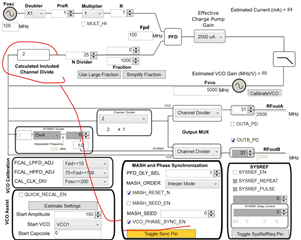

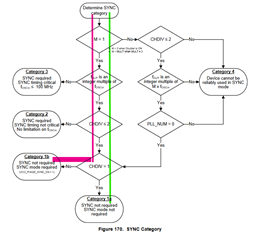

This worked fine, but the SYNC Mode didn't work as expected. We set register R0 (offset: 00h) as suggested after reset to (2118h) then to (6118h). By this setting (VCO_PHASE_SYNC_EN = 1)

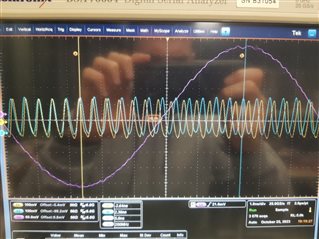

Question 2: How to exactly activate SYNC Mode, other than just setting this bit? We are getting a bizzar behavior like jumping frequency and amplitude, so not a reliable frequency as without this bit set.

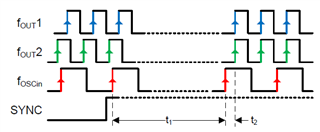

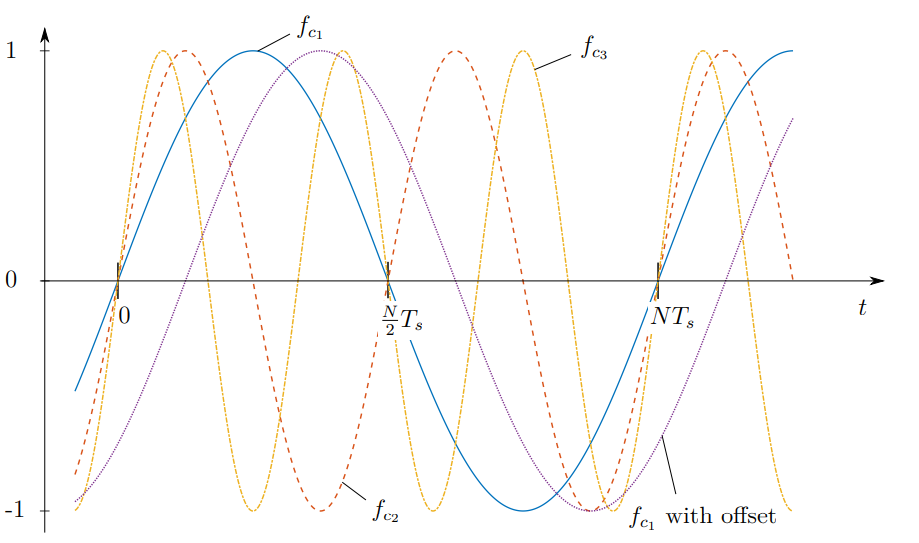

Instead we got, by the nature of the integer PLL, a synchronous behavior to the reference frequency, that was only reproducible after re-powering with an offset. Please see the pictures below:

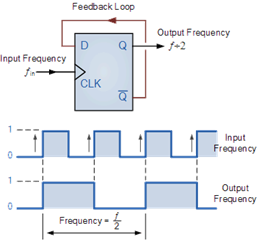

We think, this might be due to the nature of the channel divider.

By feeding back the Q' into the D Flip-Flop, the frequency gets clock divided by two, but the it depends on the intialial value of D, whether the output Q is negated in reference tothe clock or not.

Question 3: Would you maybe give an insight, how your channel divider operates? If these are as we think, then the output can only have two form and 180° offset. Could we manipulate the input of the input, to get always a similar result after repowering?

Green path:

Question 4:Why is setting CHDIV to 1 (so Channel Divider = 4) wouldn't need any Sync feature?