Part Number: LMK5C33216

Team,

My customer has the following question.

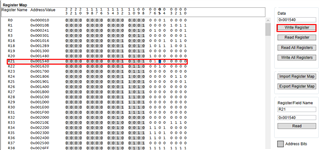

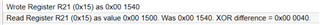

We have a question on the EEPROM of the LMK5C33216. It is working properly and we can read/write to it.

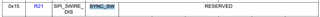

What we want to do is sanitize it, which means doing some known read and writes to verify the state of all NVM/EEPROM registers.

Our dilemma is if we write to a particular clock output and set all of it’s registers to 0x00 or 0xFF it shuts off the clock to the FPGA which is controlling/writing to the LMK.

Does the team know of a way to write to the NVM directly, without interrupting the clock(s), such that we can keep the clocks running and hence the FPGA running?

Regards,

Aaron