Other Parts Discussed in Thread: ADC12DJ3200, LMX2594, LMX2595

Dear TI team,

we are using the LMX2572 PLL to clock some fast TI ADCs.

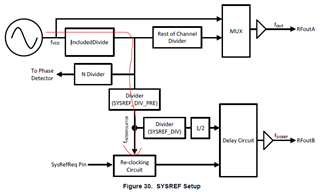

Two LMX2572 are located on two different PCBs that are provided with very low skew copies of input signals. These input signals are inherently alligned by a lower-speed PLL on each PCB first, such that SysrefReq always changes on the falling edge of OSCin, so that setup/hold times of the SysRefReq pin are guaranteed to be satisfied under all conditions.

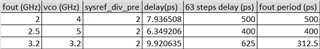

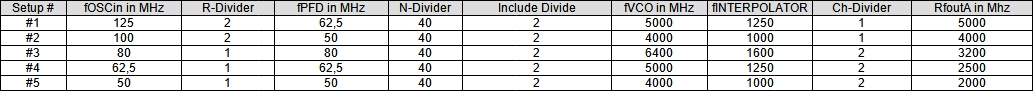

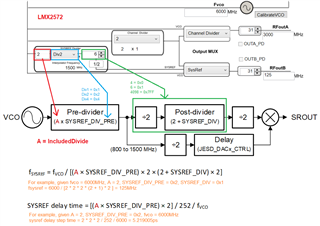

The LMX2572 is in SYSCLOCK repeat mode, currently with a SYSREF Delay of 0 steps and are configured to synthesize three different configurable frequencies of either 2.0, 2.5, 3.2 when clocking an ADC12DJ3200 or 3.2, 4.0 or 5.0 GHz when clocking an ADC5200RF.

The following setup is used for the ADC12DJ3200 and feeding it with a 2.0 GHz clock,

- f(OSCin) = 50 MHz

- f(SysrefReq) = f(OSCin) / 8 = 6.25 MHz

- Integer Mode (MASH Mode = 0)

- R_DIV = 1

- N_DIV = N' = N / 2 = 40

- Include_DIV = 2 (VCO_PHASE_SYNC_EN = '1')

- f(VCO) = 4000 MHz

- f(INTERPOLATOR) = 1000 MHz

- CH_DIV = 2

- OUTA_MUX = CH_DIV

- --> RFOutA = 2000 MHz

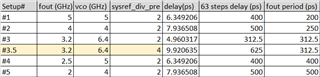

When applying the different delay values as described in the datasheet "Table 140. SYSREF Delay Step" I observed a (to me at least) weird behavior. With the setup utilizing a SYSREF_DIV_PRE = 2 the delay step is described in the data sheet being approx. 5 ps per step. I always wondered, why the LMX2572 has values depending on a divider, whilst the LMX2954 seemingly does have a constant delay step of 9ps ... but hey.

With steps of a fixed size (as the mentioned ~5ps) it would be expected, that the number of steps required to shift RefOutB (SYSREF) for a full period of RefOutA, would be different for these different periods of 312,5 ps, 400 ps or 500 ps respectively.

But when looking at RefOutA and RefOutB on a fast Scope, triggering on RefOutB, the observations with the three different setups 3.2/2.5/2.0 GHz are: applying different delays, the delay shifts by one RefOutA period (360°) with ~62 steps applied, in all the three RefOutA speeds.

How could that be, if the step size is the same for all the three different frequencies ?

Best regards

Bjoern