Part Number: LMK03328

Other Parts Discussed in Thread: USB2ANY,

Hi,

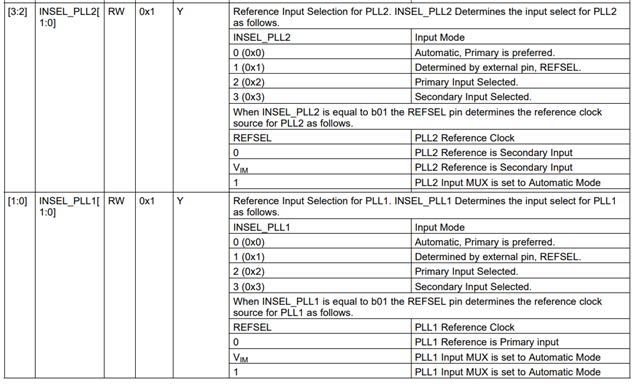

In my application, I have 2 input clocks, only one of which is active at any given time, and 2 different output clocks which are always active.

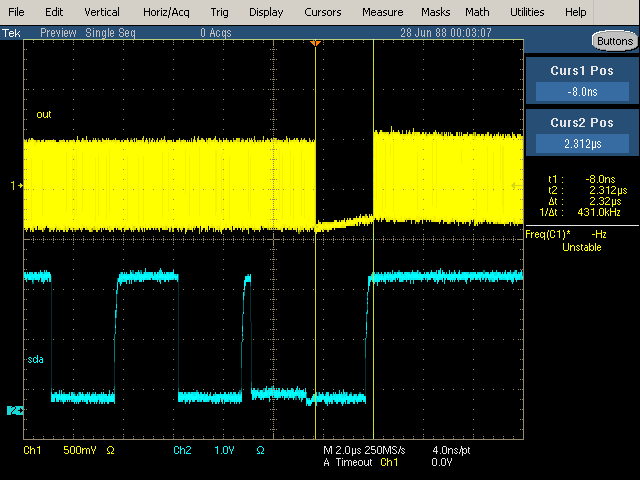

I need to switch between input clocks as fast as possible.

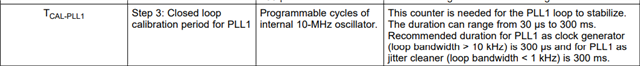

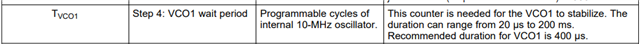

- Jitter requirements are assumed to be relaxed. PLL bandwidth can thus be higher to reduce lock time. Can you comment on an order of magnitude for the lock time? I know this depends on many parameters, but I need some input for a feasibility analysis.

- I can either store 2 configurations in ROM and switch between those or do the minimum necessary adjustments over I2C. Can you comment on time budget of both solutions?

- The PLL will need some reset to calibrate the internal VCO when switching configuration Can you comment on time budget of this reset?

Thank you very much for input!