Hi there!!

I am using LMX2594 and want to use a sync mode.

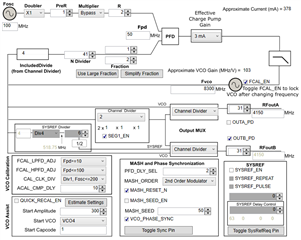

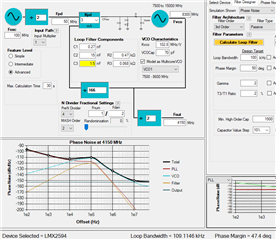

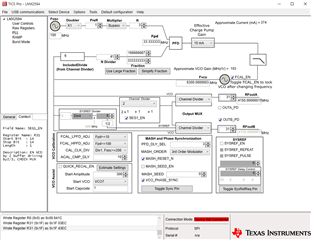

I have set the PLL as the pic below

There is a problem I want to fix.

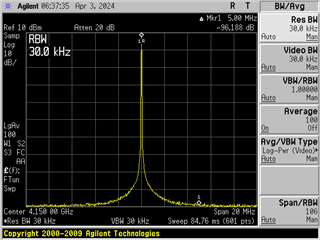

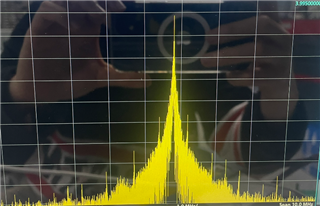

When I set fractional mode which is the output of PLL is not a multiple of Fosc,

(For example Fosc : 100 MHz, Output : 4050Mhz)

The output of PLL looks like there is a fractional spur like below

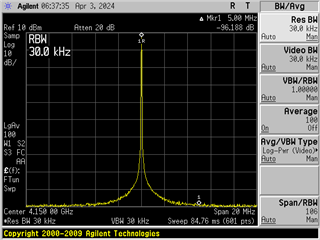

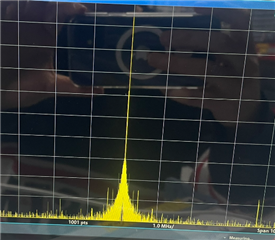

And It doesn't happen If I use integer mode which is the output of PLL is a mutilication of Fosc.

(For example Fosc : 100 MHz, Output : 4000Mhz)

It looks very clean like below.

This issue specifically occurs only when in sync mode. (when VCO_Phase_Sync = 1)

Anyone know about this problem or how to fix?

Thanks