Hello

I am using the LMK03806BISQE_NOPB part on my board.

The uWire is working; it was tested by toggling the FTEST/LD as per the suggestion in the datasheet.

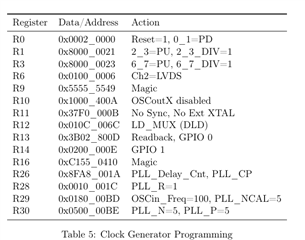

I am loading registers as per the attached figure. The relevant schematic is also shown below.

For the time being I am interested only in CLK2. The other outputs can remain disabled.

There is no output at CLK2, and in addition the LD on pin 33 is remaining low.

Any ideas on finding the fault here?

Thanks for any help.

David