Tool/software:

Hi all,

In our application, we need to dynamically control the phase of a clock respect to the relative data.

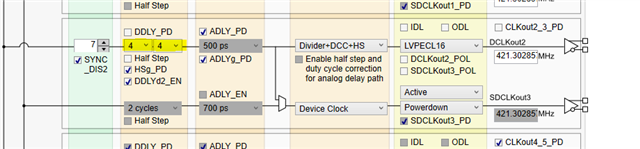

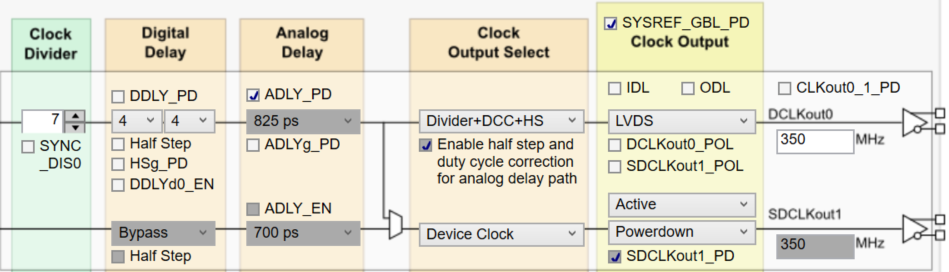

For this application we are trying to use the LMK04828 (using the relative demo board LMK04828EVM) and we followed the datasheet configuration for a 350MHz input and output clock with zero delay mode.

Outputs are sync with the input.

We are correctly able to apply an analog delay but the problem is with the digital delay:

We are not able to control in a "stable" way the advance or the delay of the clock with digital delay.

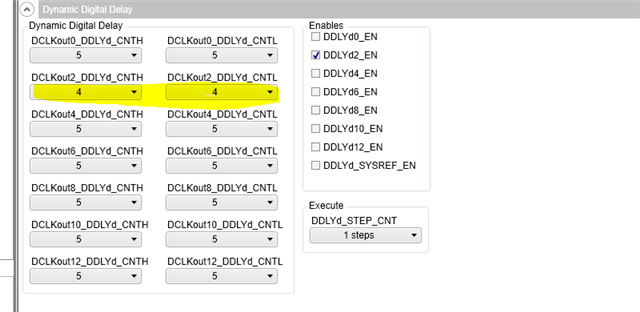

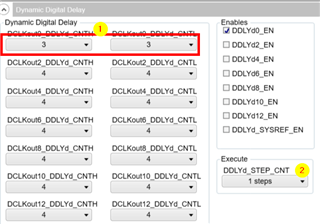

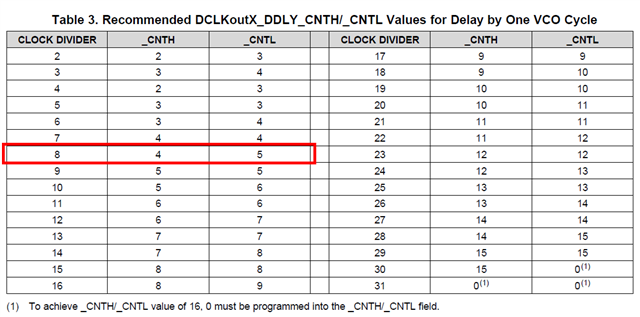

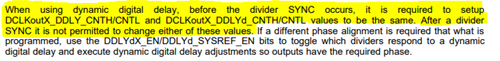

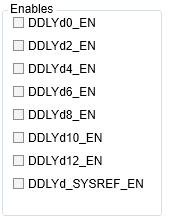

The clock use an internal divider of 7 and so following the procedure described at section "9.3.3.2 Dynamic Digital Delay" and we set values for DCLKoutX_DDLY_CNTH/_CNTL to have 1 single step of delay :

TO GO FORWARD : _CNTH = 4 and _CNTL = 4

TO GO BACKWARD: _CNTL = 3 and _CNTL = 3

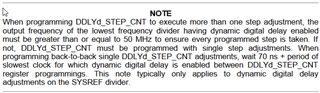

and after we applied a DDLYd_STEP_CNT = 1, expecting that this provide each time 1 simple step of the clock phase or forward or backward (depending on the previous DDLY_CNTs)

Unluckily doing an automatic test that moves the clock 3 steps forward and 3 backwards we notice that sometimes there is an unexpected shift with one of the step that is DOUBLED, resulting in a total of 4 steps in advance (or in delay) instead than the expected 3.

For us is mandatory to have a stable and predictable phase delay.

Is there something wrong in the configuration?

is there something else we could try or is this an expected behavior ?

thanks in advance.