Other Parts Discussed in Thread: LMK04828, LMK04616

Tool/software:

Hi,

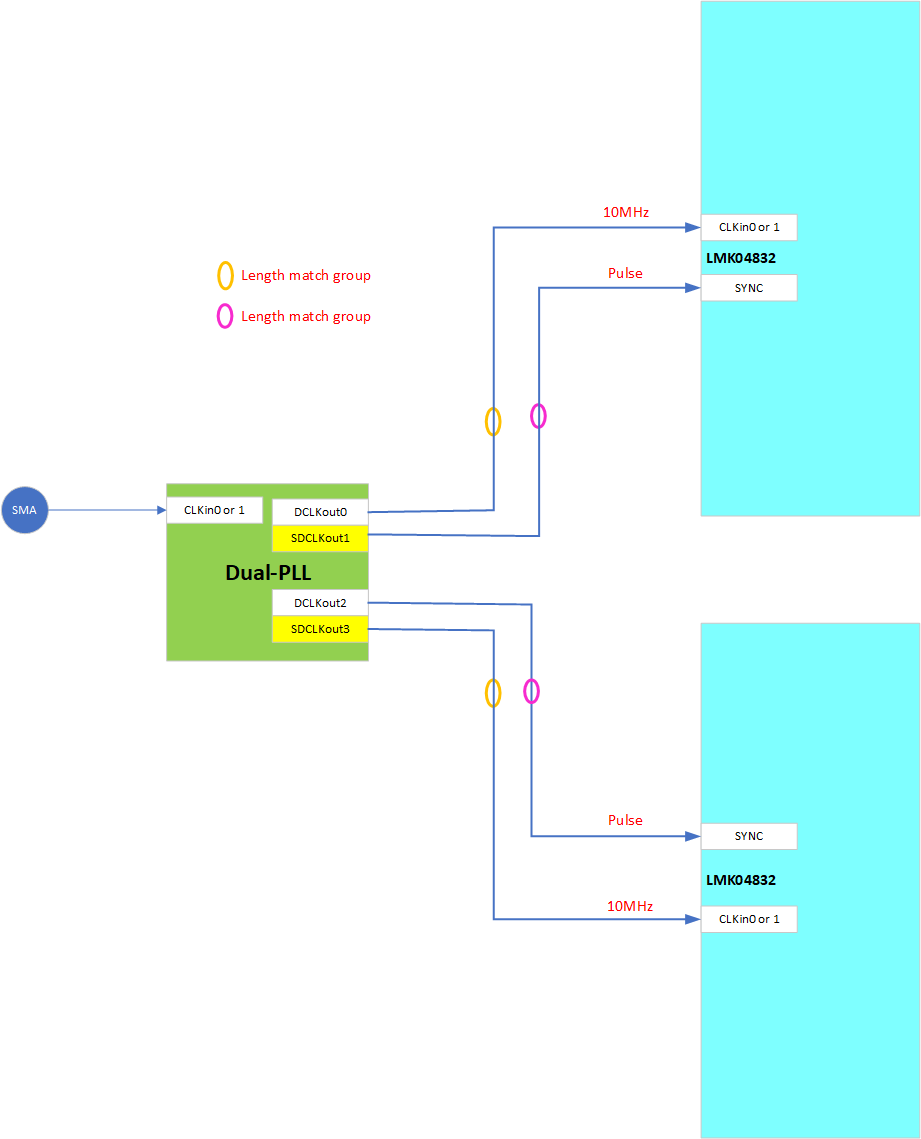

I have a question about how to provide sync pulse to multi-chip of LMK04832:

Need SYNC pulse to be synchronized to reference clock to LMK04832? Could below two schemes get the same synchronization accuracy?

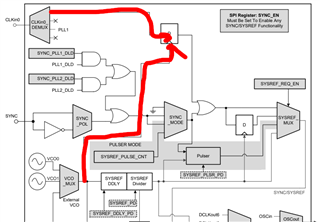

As below figure.1 shown, reference clock and Sync pulse all come from another dual-PLL such as LMK04828 or LMK04832. Under this case, Sync pulse from SDCLKout of dua-PLL is synchronous to DCLKout which is reference clock to CLKin of next LMK04832

Figure.1

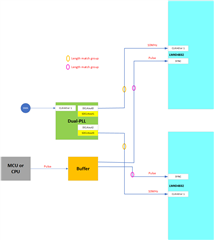

As below figure.2 shown, sync pulse come from MCU or CPU through Buffer fanout. This sync pulse are asynchronous to reference clock of next LMK04832 totally.

Figure.2

Thanks in advance!

Best regards!

Jason