Part Number: LMK04821

Tool/software:

I've been trying to work out the delay between the SYSREF and DEVCLK outputs for the LMK04821 device, however my calculations based on the formulae in the datasheet don't seem to match the value I've measured on our board.

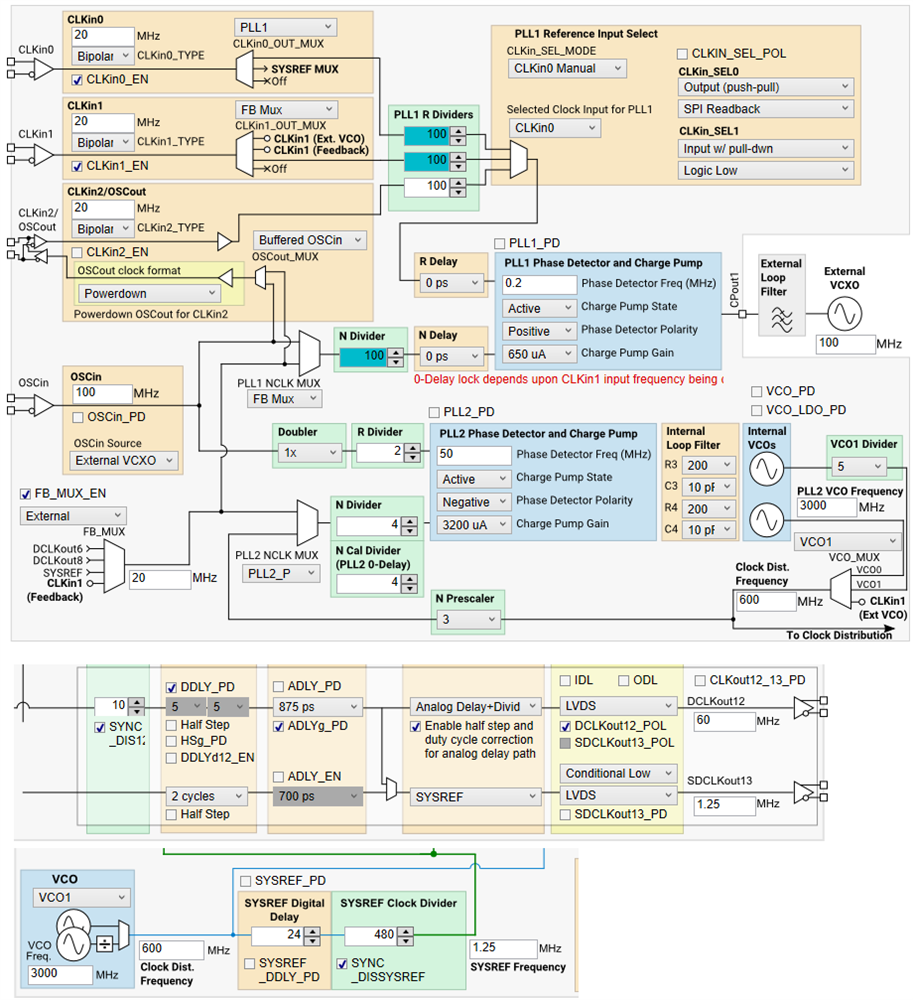

I've attached the TCS file from TICS Pro for our setup.

We have these settings for the LMK. Using nested zero-delay mode, with a 100MHz VCXO for PLL1 and the internal VCO1 with /5 prescalar to get a 600MHz PLL2 VCO frequency. The external feedback is coming from DCLKOUT6 fed back in to CLKIN1. This appears to be working as expected (input to output delay is ~0ns) and both PLLs are fully locked.

We use the external sync pin to synchronise all the output dividers, then once fully locked, use the sync pin again to send out a set of four SYSREF pulses at 1.25MHz.

Using a pair of differential probes, I've measured a latency of -4.1ns between the DEVCLK rising edge and the rising edge of the SYSREF signal. That is to say the SYSREF rises 4.1ns before a DEVCLK edge.

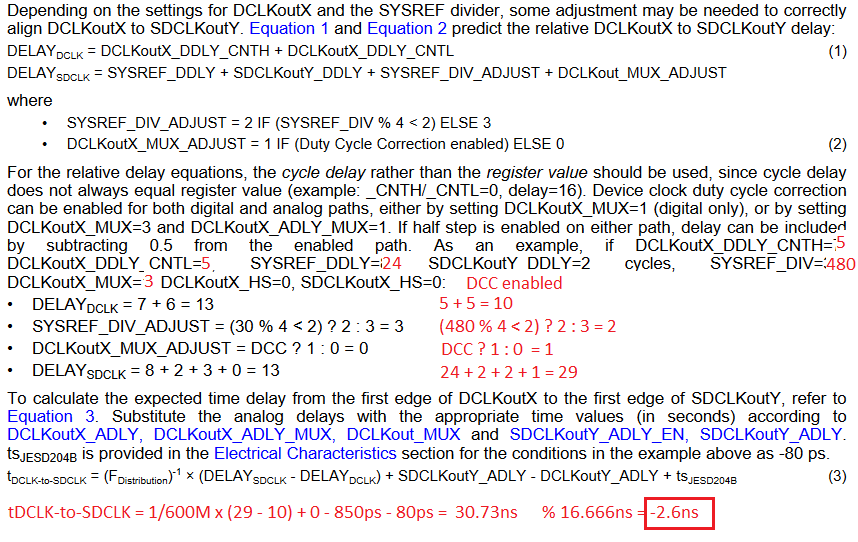

Based on the datasheet, section 9.3.4 SYSREF to Device Clock Alignment, using the various register settings above, I calculate that the latency "Tdclk-to-sdclk" should be 45.73ns. If we subtract the period of 3 DEVCLK cycles from that, the formulas suggest the delay should be -2.6ns. using the following information:

Note that DCC is enabled because in some configurations we use 120MHz (/5) rather than 60MHz (/10), and want a consistent delay in both cases.

Could you provide any insight as to where I have gone wrong in my calculations?