Other Parts Discussed in Thread: ADC12DJ3200, LMK04828, LMK04832, LMK04808

Question,

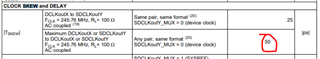

If trace lengths are matched, what are the correct delays for two pairs of DEVICE and SYSREF clocks going to an FPGA JESD block and the ADC12DJ3200?

The ADC dev clock is running at 3 GHz, the FPGA dev clock 300 MHz, and the SYSREF clock at 18.75 MHz.

Edit:

Sorry this is for the LMK04828

I reposted here: https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1165773/lmk04828-devclk-and-sysref-delays