Tool/software:

Hi,

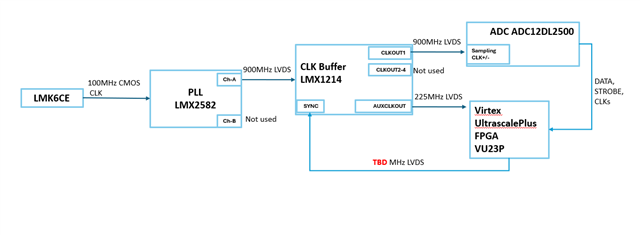

We have an implementation as below and a requirement to have a common clock source for both ADC sampling clock and FPGA.

Since FPGA cannot take 900MHz input (from CH-B of PLL or CLKOUTS2-4 of ClkBuffer), we plan to use 225MHz LVDS from AUXCLKOUT pins of clock buffer.

Per my understanding to sync the outputs of CLKOUT1 and AUXCLKOUT: SYNC pin is mandatory.

1) Is that correct?

2) If yes, we are thinking of sending the SYNC input along with the clock buffer configuration settings which will be programmed thru' SPI at the start of the Clock buffer.

Can you pls confirm that ONE SYNC trigger is sufficient to be sent from FPGA at the buffer startup along with other SPI config settings?

3) Is there any frequency requirement for this SYNC LVDS trigger input to Clockbuffer?

Thanks