- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

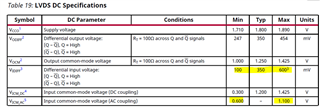

I have a differential 225MHz clkout to FPGA. LVDS Input side AC-coupling requirement in FPGA is highlighted.

What is the power out dBm need to choose for clkout to meet the FPGA input voltage requirement?

Thanks

Hi Noel,

No - I mean the CLKOUT only not the AUXOUT. Input clk is 1800MHz for CB. We can divide by 8 and take it out as 225MHz for the FPGA.

FPGA accepts AC-coupling for LVDS. Hence we plan to connect the CLKOUT to FPGA.

What would be PWR setting in that case?

Also, can you recommend the proper termination for CLKOUT while connecting to FPGA?

Hi Nandini,

If you use CLKOUT, you have to AC-couple it to the FPGA.

PWR =2 voltage swing is 420mV.