Other Parts Discussed in Thread: CDCE913, CLOCKPRO

Tool/software:

Dear Expert,

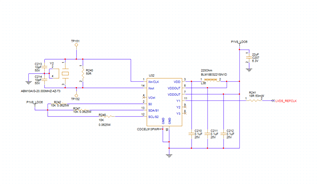

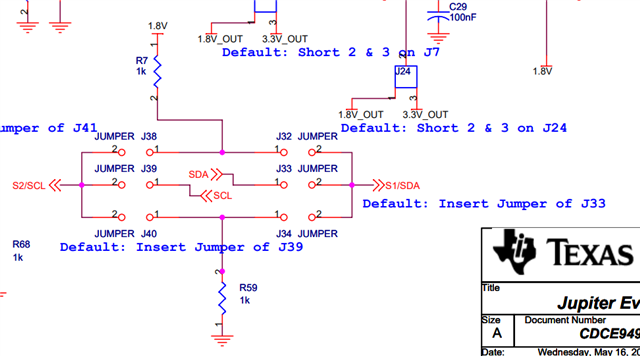

After generating the register values through TI's Clock Pro Software and programming the IC using ADB I am unable to generate the desired 63 MHz frequency.

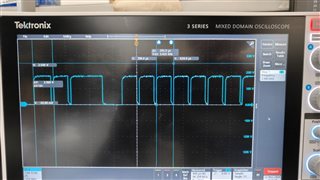

Attached image below shows that I am only able to generate 3-4 KHz even though my input from crystal oscillator is 20 MHz.