Other Parts Discussed in Thread: LMK00804B,

Tool/software:

Dear,

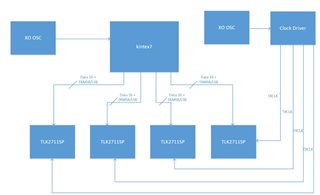

I'll use TLK-2711SP with kintex7 fpga like below figure.

Unfortunately, FPGA clocks have poor jitter characteristics. So, I think I will try to design it as shown in the picture below.

How can I match the timing of Clock and Data?

Best regards,