Tool/software:

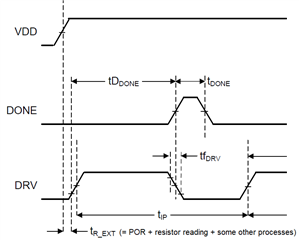

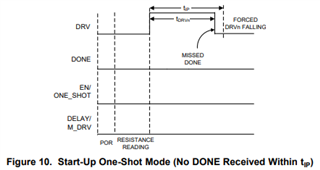

The datasheet for this PN references POR and "Resistance Reading" time (t_Rext). t_Rext is typically 100ms with a maximum of 120ms. I'm performing a worst case analysis based on timer accuracy and external delay resistors to better understand what range of time we'd expect out of the DRVn pin. Is there a minimum value for t_Rext? Can you all define t_POR? I need to know min/max time that it would take this device to start the timer.