Other Parts Discussed in Thread: ADC12QJ1600

Tool/software:

Hi Team,

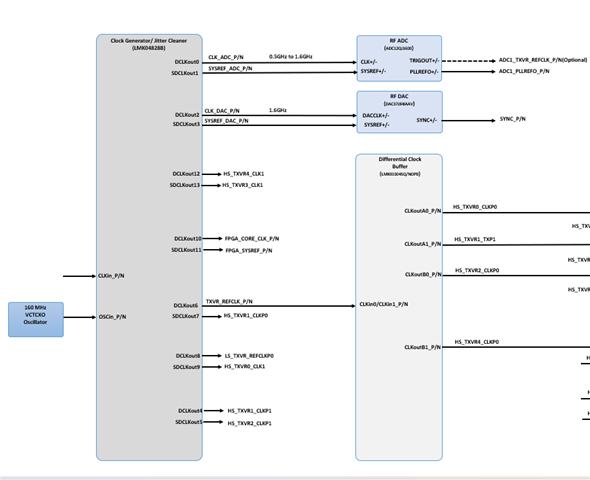

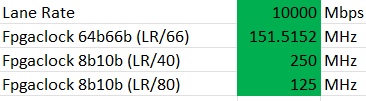

I want to interface the LMK04828B Clock Generator, ADC12QJ1600AAVQ1: Analog to Digital Converter (ADC), and DAC37J84IAAV: Digital to Analog Converter (DAC) with the Altera Agilex 5 device.

May I know what will be the clock requirements, such as device clock and sysref for ADC and DAC? As well as what is the range of clock frequencies that needs to be supported for FPGA reference clocks.

Regards,

Liston