Other Parts Discussed in Thread: USB2ANY, , LMK05318, LMK5B33216

Tool/software:

We have implemented the LMK05318B for use in a digital carrier board, to provide a reference 40 MHz set of signals to an RFIC and FPGA. We use a 24 MHz XO that has a +/- 2.5ppm accuracy and a GPS receiver from u-Blox to provide a PPS input.

I'm attaching our TCS file: https://drive.google.com/file/d/1yKAOyZ3CsoECdfFrOq-e86CL_EgNNyhQ/view?usp=drive_link

And the carrier board's schematic page: https://drive.google.com/file/d/1t9dCRsU3_SJ7NDb1n1_-0KC1_oprw6b2/view?usp=sharing

We have the following status bits when we flash our LMK chip:

- 'LOL_PLL1': 1

- 'LOL_PLL2': 1

- 'LOS_FDET_XO': 0

- LOS_XO': 0

- 'HIST': 0

- 'HLDOVR': 1

- 'LOFL_DPLL': 1

- 'LOPL_DPLL': 1

- 'LOR_AMP': 0

- 'LOR_FREQ': 0

- 'LOR_MISSCLK': 0

- 'REFSWITCH': 0

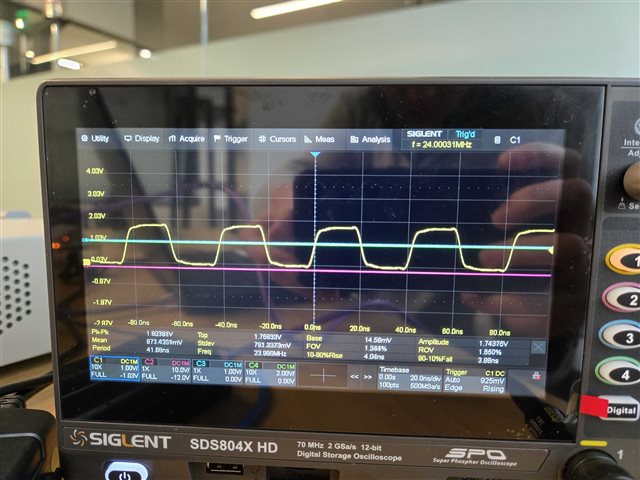

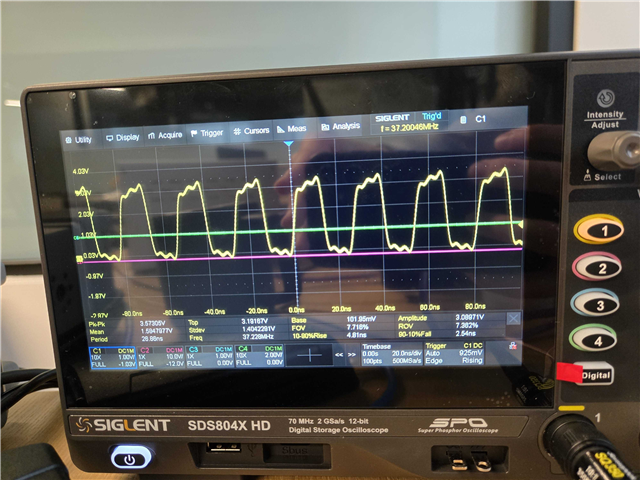

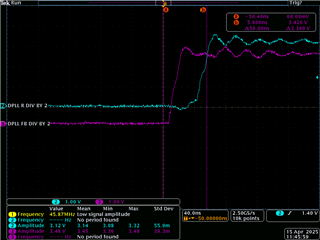

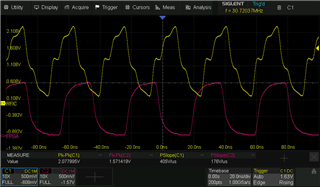

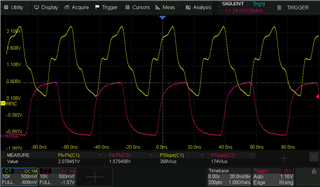

Meaning that our LMK chip's DPLL cannot lock on, even after waiting for several hours (~12 hours) to the lock to be established. We have measured the pps signal and XO input and they are valid signals, using an oscilloscope. The LDO power supplies are working properly.

Any input and recommendations to achieve a DPLL lock would be appreciated, or further debugging steps.