Tool/software:

I want to use a master LMK04828 to generate 7.8125M clock and input it to the in0 port of two LMK04828 chips for multi-board synchronization.

The clocks of the two slave machines I tested were basically synchronized but the frequency seemed unstable and there was a lot of jitter

Master/slave LMK circuit schematic diagram, the slave LMK only uses the 100M crystal oscillator on the board and the IN0-7.8125M output of the master LMK

The 7.8125M output of the host LMK and the output of the active LMK are synchronized without jitter and connected to the in0 port of the slave LMK through an equal length coaxial cable

The output of the slave LMK 500M is biased and jitter

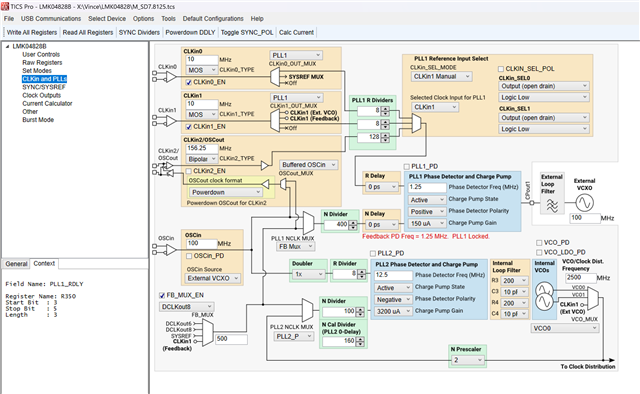

The configuration file of the slave machine

I am not very clear about the configuration of multi-board clock synchronization. I hope you can guide and help me!