Tool/software:

Hi TI forum,

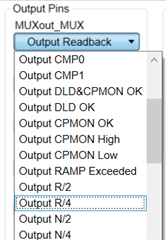

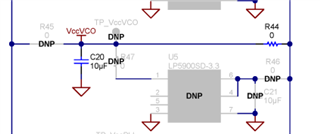

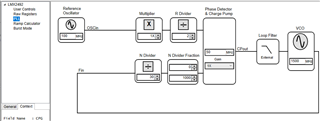

I have just connected an external VCO by removing R6 and R4_LF, and connecting RF_out's SMA to VCO RF_out divided by 16 (24 GHz VCO to 1.5 GHz DIV) and Valf to VCO's Vtune. Also I have changed the values of the passive filter using PLLatinum SIM. In TICS Pro I have configured the PLL tab like this:

VCO output is -10 dBm, but from what I have read in this thread is fine (https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/742862/lmx2492-power-level-for-fin?tisearch=e2e-sitesearch&keymatch=LMX2492%25252525252520fin#). And, Vtune, has a range from 0 V to 1.8 V.

VCO just connected and without Vtune voltage operates at 1.387 GHz, but the desired frequency is 1.5 GHz, and my objective is to do ramps from 1.5 to 1.516 GHz.

When running that configuration, D1 LED doesn't turn on and PLL doesn't generate the 0.88 V needed to set the VCO frequency to 1.5 GHz. Also, Vtune is a flat signal at 0 V with random peaks of 1.8 V

I would like to know if any other configuration is needed to configure the PLL to work as expected.

I can share more info if needed.

Thanks in advance,

Joaquín